# Alfaskop System 41

# **Technical Description**

**Text Section**

#### **Preface**

This is the text section of the Technical Description for Alfaskop System 41. Its objective is to describe the main functions carried out by the logic of the display units, the flexible disk units and the communication processors as realized by the printed circuit boards.

Chapter 1 serves as general information on the system. Functions or circuits common for two or more units are described in chapter 2 and 3. The other chapters deal with specific units or logic boards.

Certain information is quoted from Motorola Inc. publications.

For information on printers and flexible disk drives, please refer to separate documents. Titles and Printed matter numbers can be found in the Service Information binder under Index of Current Literature.

Tips for the reader:

- A byte consists of eight bits if nothing else is said.

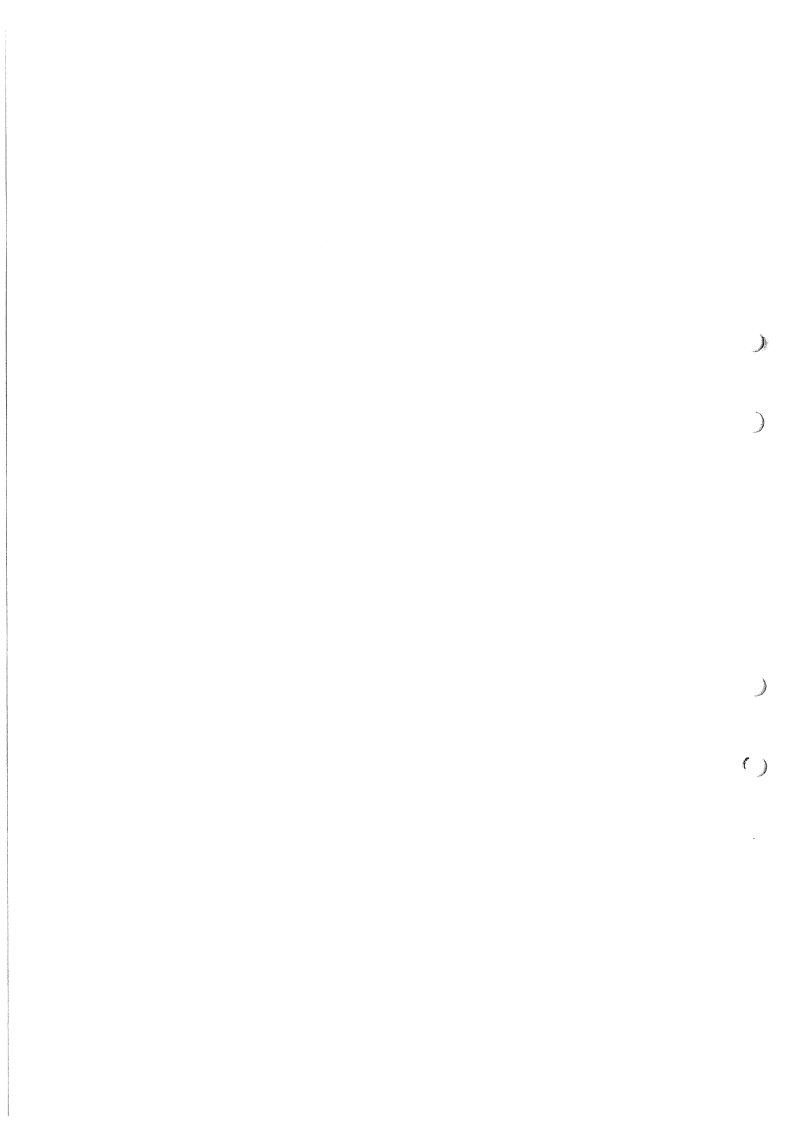

- Bit 0 always designates the least significant bit of a word. E.g. bit 7 (for data) or bit 15 (for addresses) is the most significant bit. Bit is often written b, e.g. b7 means bit 7.

- X or in register descriptions normally means don't care bits.

- A pin of an integrated circuit or of a connector and sometimes a bit in a register is indicated as a number after a colon. E.g. pin 12 of IC25 will be written as 25:12, pin 2 of connector P1 could be indicated as P1:2.

- A bar over a signal name or a circle on a drawing of a wire or before a signal name indicates that low level is active (or negative logic for buses). E.g. "Bus addressing means that addressing from bus takes place when the signal "Bus addressing is low.

The specifications in this publication are subject to change and supplementation without notice.

It is possible that this manual contains information on Alfaskop products or functions no longer or not yet available in your country. This shall not be construed to mean that an announcement of such Alfaskop products or functions will be made in your country.

This is a revised edition of publication E9000 3062E-2. A new chapter Display Unit, DU 4113, has been added. The chapters 7, 9, 13, 15 - 16, 19 - 20 and 22 - 23 will be updated as soon as possible but until then, some of the references to the Microcomputer chapter are actually found in the Communication or Power Supplies chapters.

©1984, Ericsson Information Systems AB, Data Terminals Documentation S-175 86 Järfälla, Sweden

## **Reader comments**

You can help improve future editions of this document by answering the following questions and sending us your comments.

|    | Document name and number:                                                  |

|----|----------------------------------------------------------------------------|

|    |                                                                            |

|    |                                                                            |

| 2. | My job:                                                                    |

|    |                                                                            |

|    |                                                                            |

|    |                                                                            |

| 3. | I have used this document                                                  |

|    | ☐ To acquire general information (for ———————————————————————————————————— |

|    |                                                                            |

|    | ☐ As a technical manual (reference book)                                   |

|    | ☐ As a textbook in a course (trainee)                                      |

|    | ☐ As source material for teaching a course (instructor)                    |

|    | Comments:                                                                  |

|    |                                                                            |

|    | •                                                                          |

| 4. | I think this document is                                                   |

|    | ☐ Easy to find things in                                                   |

|    | ☐ Easy to find things in with some reservations                            |

|    | □ Difficult to find things in                                              |

|    | Comments:                                                                  |

|    |                                                                            |

|    |                                                                            |

| =  | I think this document is                                                   |

| э. | •                                                                          |

|    | ☐ Easy to understand                                                       |

|    | ☐ Easy to understand with some reservations                                |

|    | ☐ Difficult to understand                                                  |

|    | Comments:                                                                  |

|    |                                                                            |

| ,  |                                                                            |

| 0. | I think this document is                                                   |

|    | ☐ Well illustrated                                                         |

|    | ☐ Poorly illustrated                                                       |

|    | Comments:                                                                  |

|    |                                                                            |

|    |                                                                            |

| 7. | I think that this document provides                                        |

|    | ☐ Full coverage of the subject at hand                                     |

|    | ☐ Poor coverage (essential parts are lacking)                              |

|    | Comments:                                                                  |

|    | 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그 그                                      |

| 8. | I think that this document is               |

|----|---------------------------------------------|

|    | ☐ Well adapted to my skills and knowledge   |

|    | ☐ Poorly adapted to my skills and knowledge |

|    | Comments:                                   |

|    |                                             |

| _  |                                             |

| 9. | Other comments:                             |

|    |                                             |

|    |                                             |

|    |                                             |

We appreciate your cooperation. Please send your answers and comments to

Ericsson Information Systems AB Alfaskop Documentation Department S-175 86 Järfälla, Sweden

# **General Concepts**

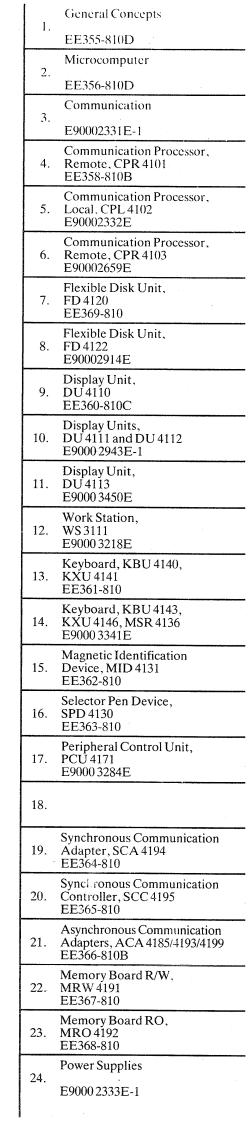

# Contents

| Introduction                | 1 |

|-----------------------------|---|

| System Architecture         | 1 |

| Some Configuration Examples | 1 |

| Abhreviation List           | 6 |

#### Introduction

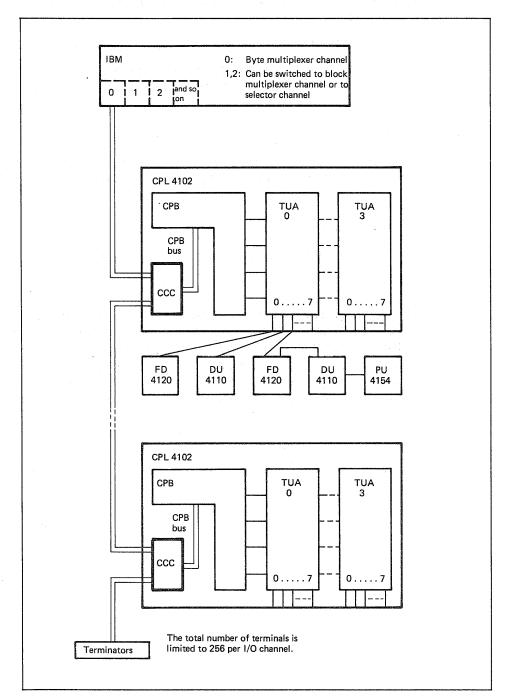

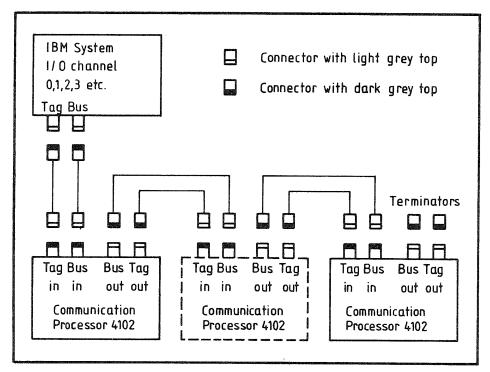

This chapter contains a brief presentation of the hardware components of Alfaskop System 41. For detailed information on combination possibilities for different emulations (IBM 3270, UTS 400 etc.) look in the respective reference manual.

### **System Architecture**

#### **Some Configuration Examples**

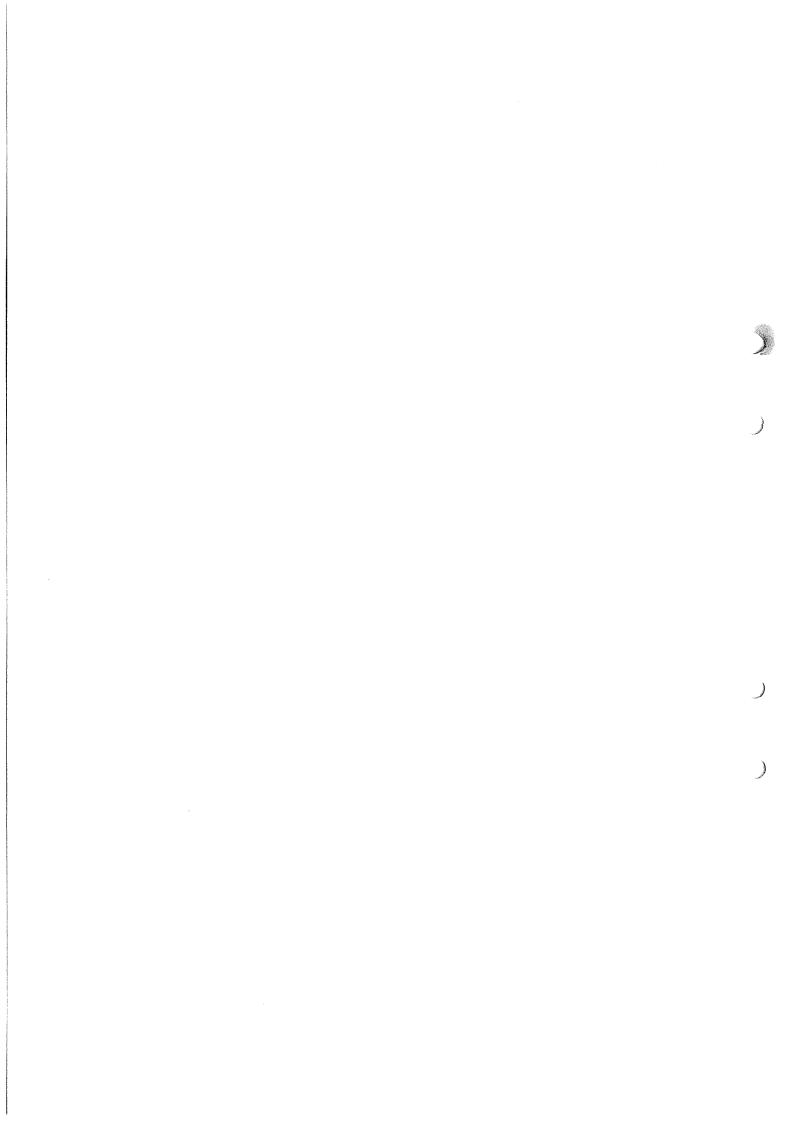

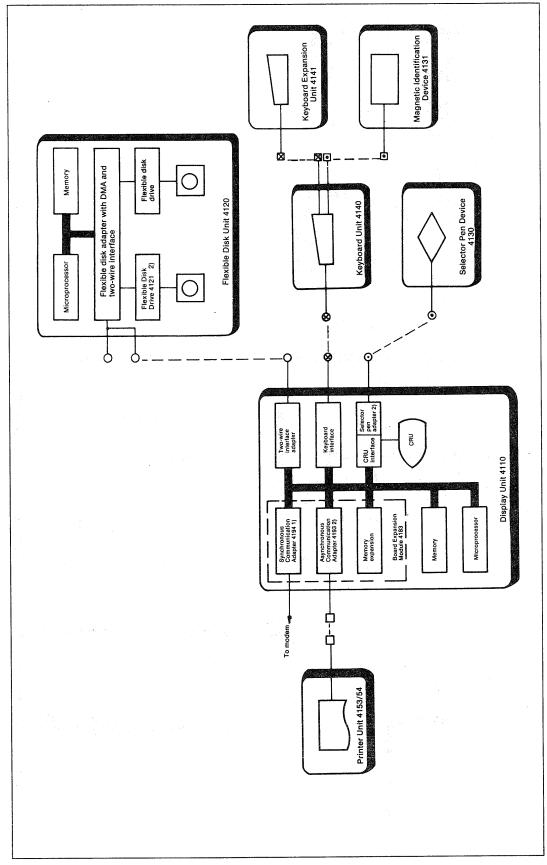

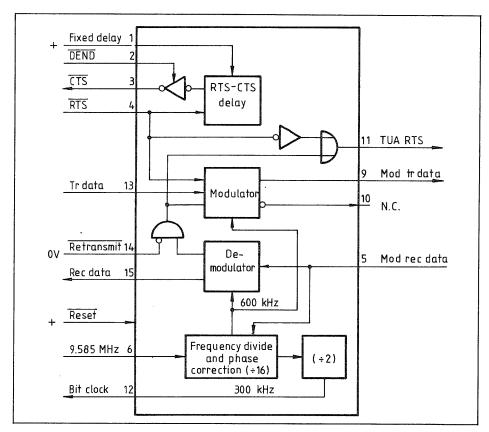

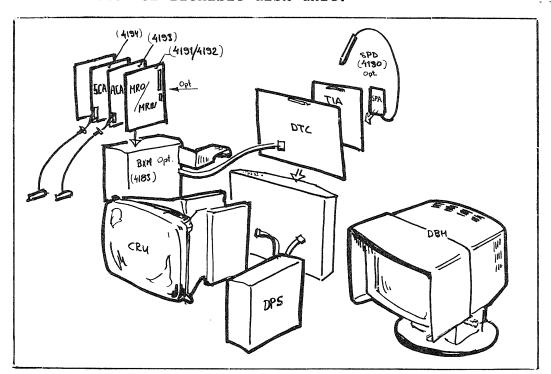

Fig. 1 shows a single display unit connected to a computer via modem and telephone lines (remote connection). Descriptions of modem interface logic boards are found in the SCA and ACA chapters.

Fig. 1. Example of single display unit configuration

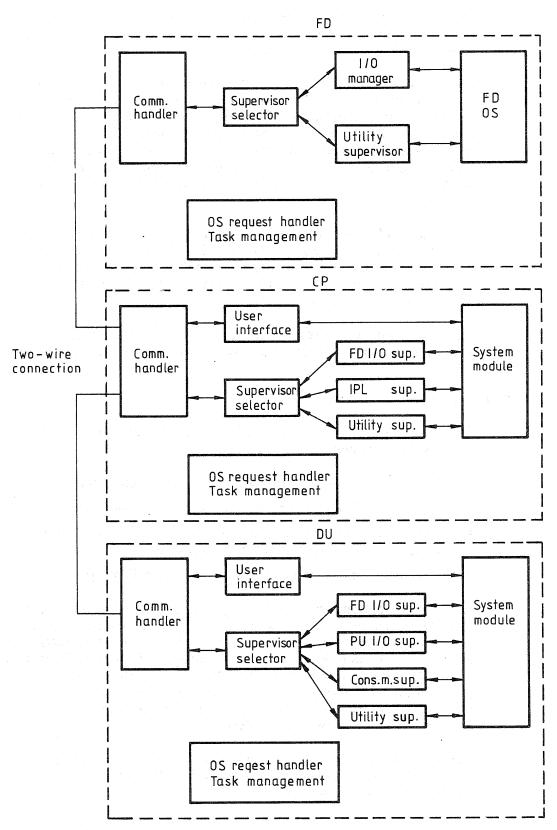

A flexible disk unit is connected to the display unit via a two-wire cable. A coarse description of the two-wire interface of the system units can be found in the Microcomputer chapter. A printer is connected to the display unit via a V24/V28 cable.

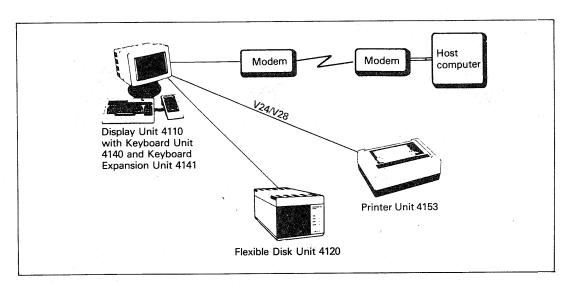

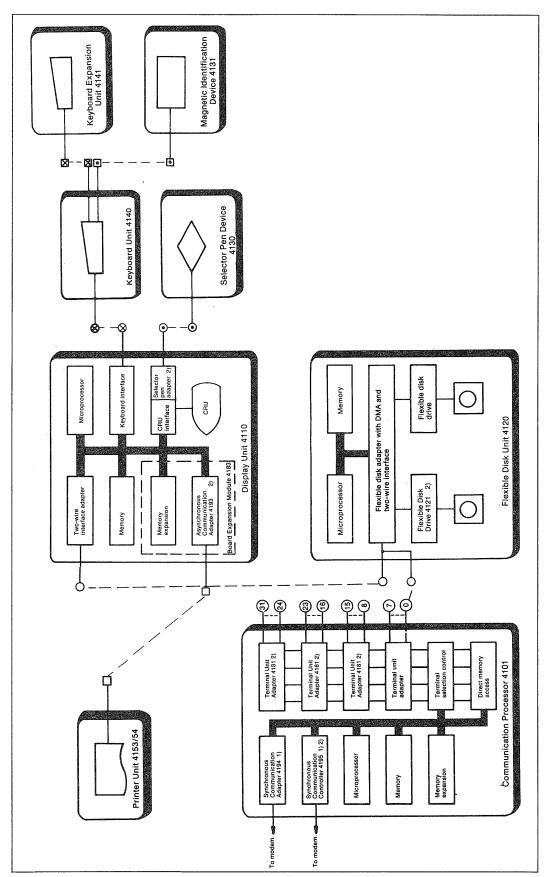

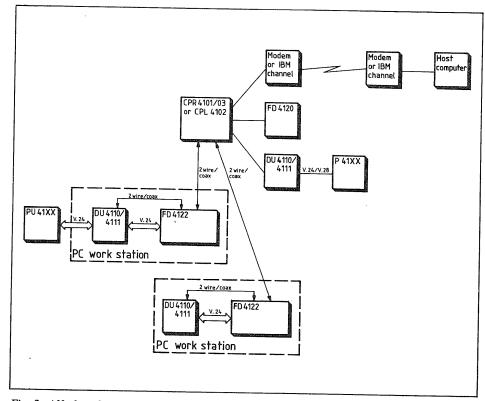

Fig. 2. Example of terminal cluster connected remotely to host computer

Fig. 2 shows an example of a cluster configuration (more than one terminal using the same line to communicate with a computer). The communication processor communicates with display units and flexible disk units via two-wire cables. The printers are connected to display units via V24/V28 cables.

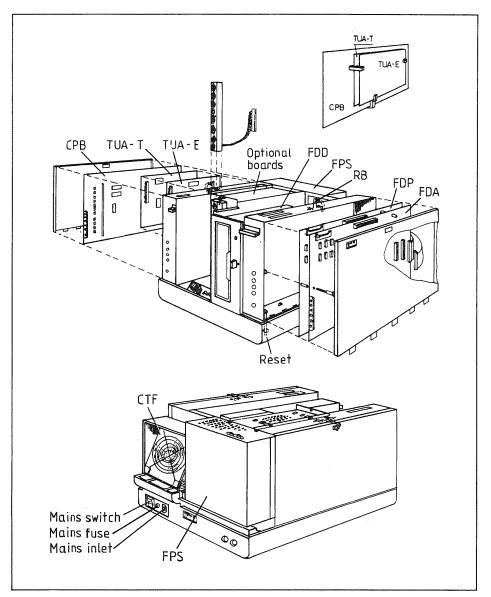

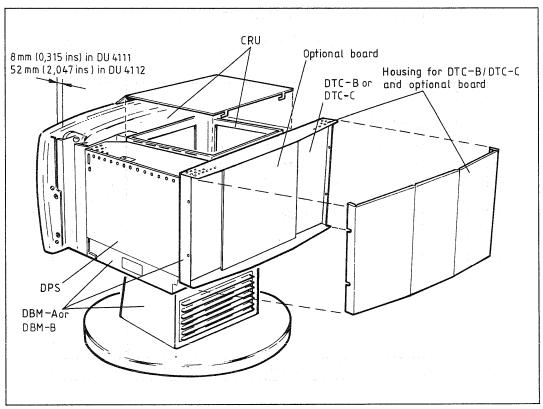

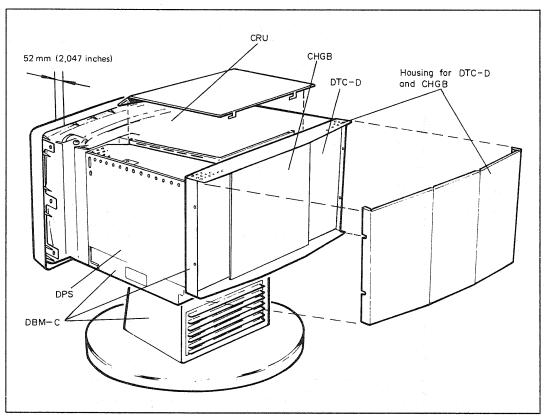

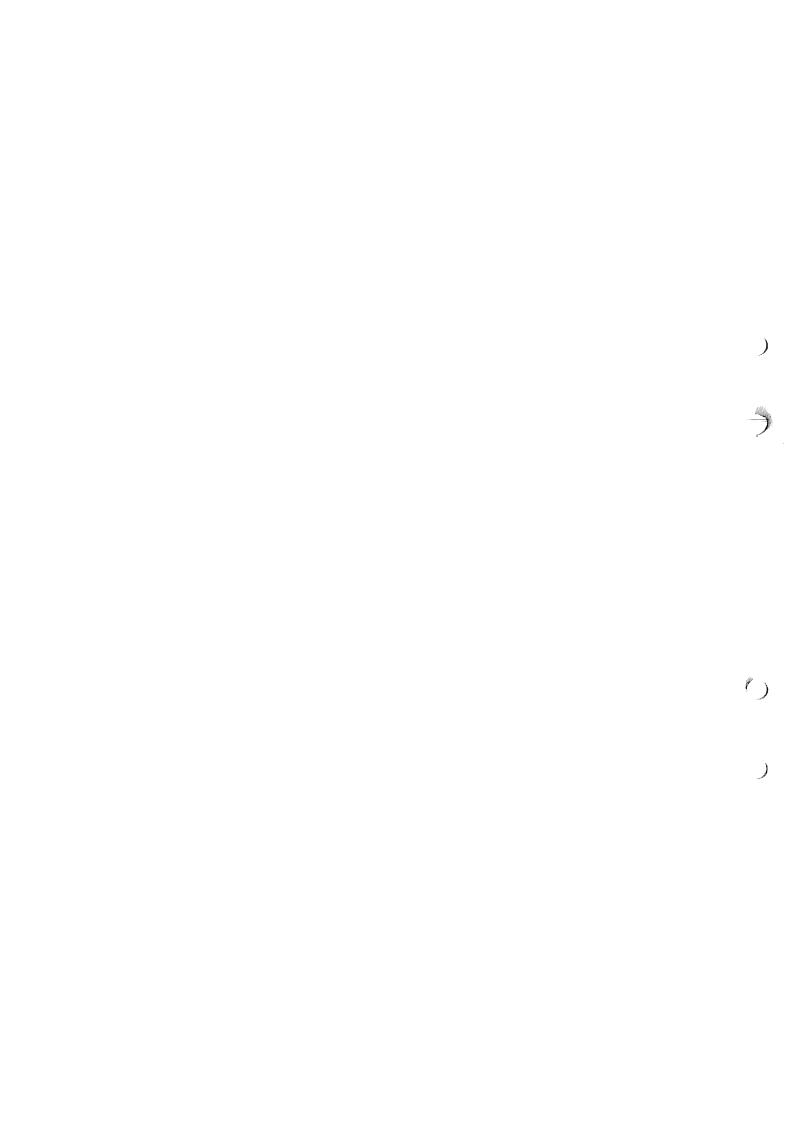

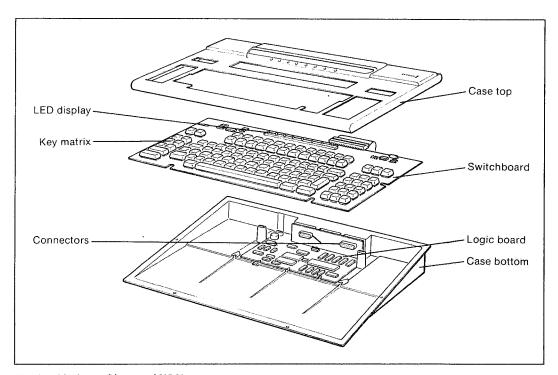

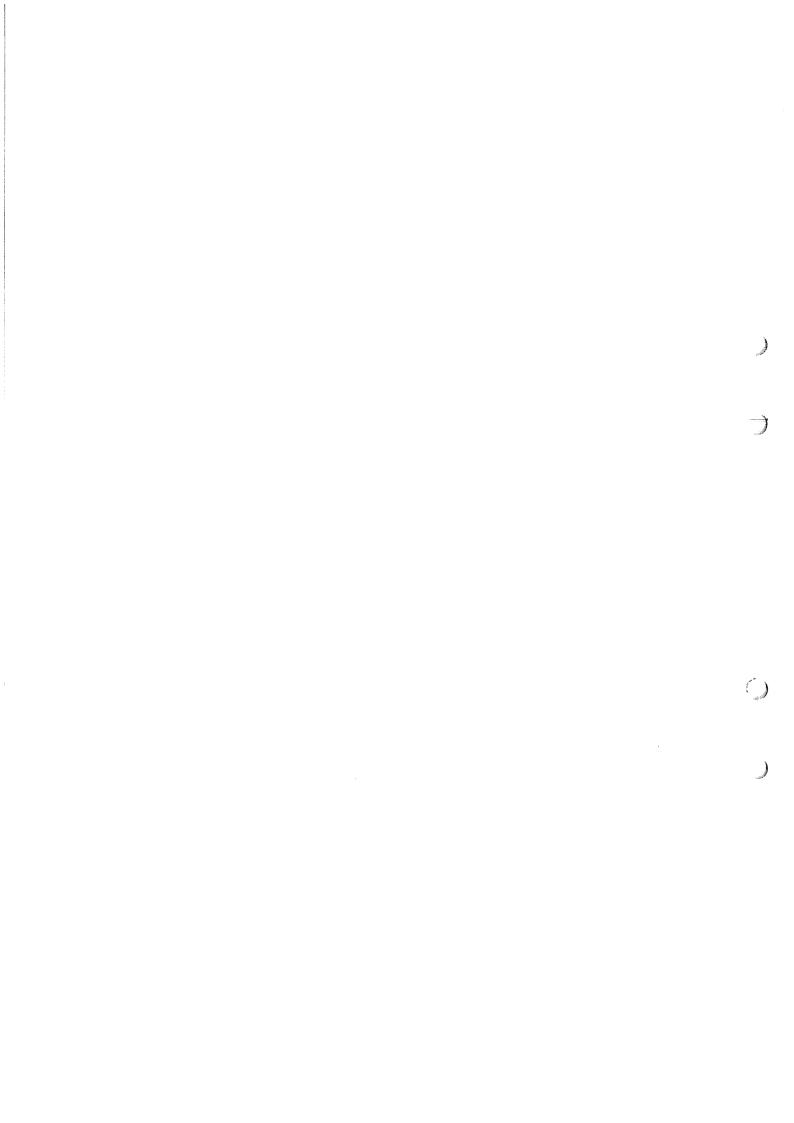

Fig. 3 shows some of the components of units used in single configurations.

Fig. 3. Single display unit configuration details

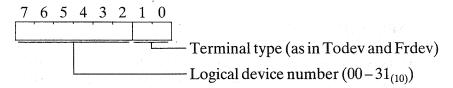

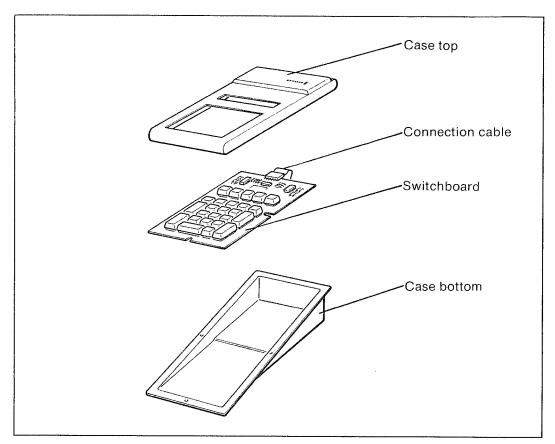

Fig. 4 shows the components of units used in remote cluster configurations. Note that a communication processor for remote connection to a host computer (CPR) is shown.

Fig. 4 Remote cluster configuration details

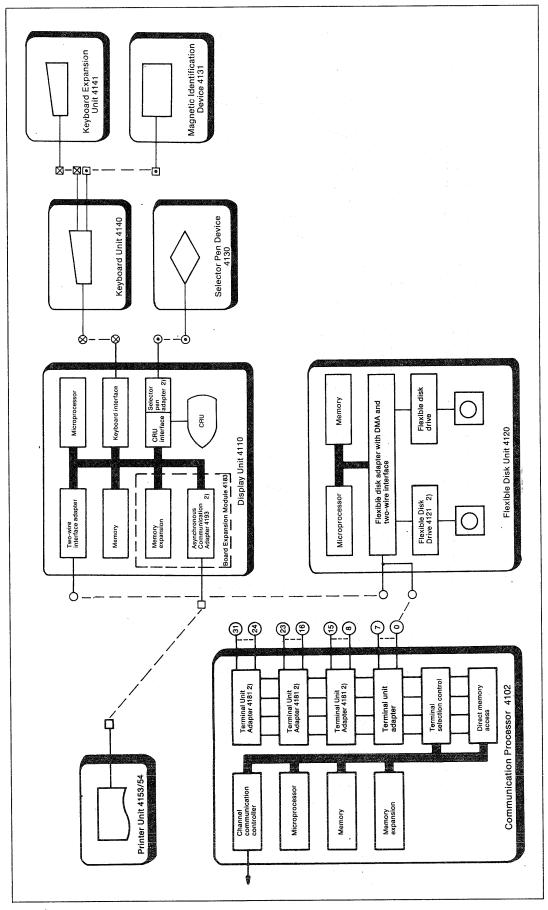

Fig. 5 shows the components of units used in local cluster configurations.

Fig. 5 Local cluster configuration details

#### **Abbreviation List**

ACA = Asynchronous communication adapter

BXM = Board expansion module

CCC = Channel communication controller

CIB = CCC interconnection board CP = Communication processor

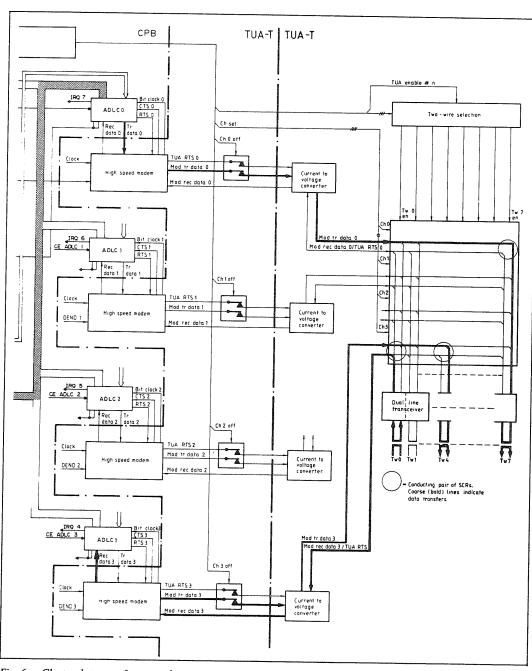

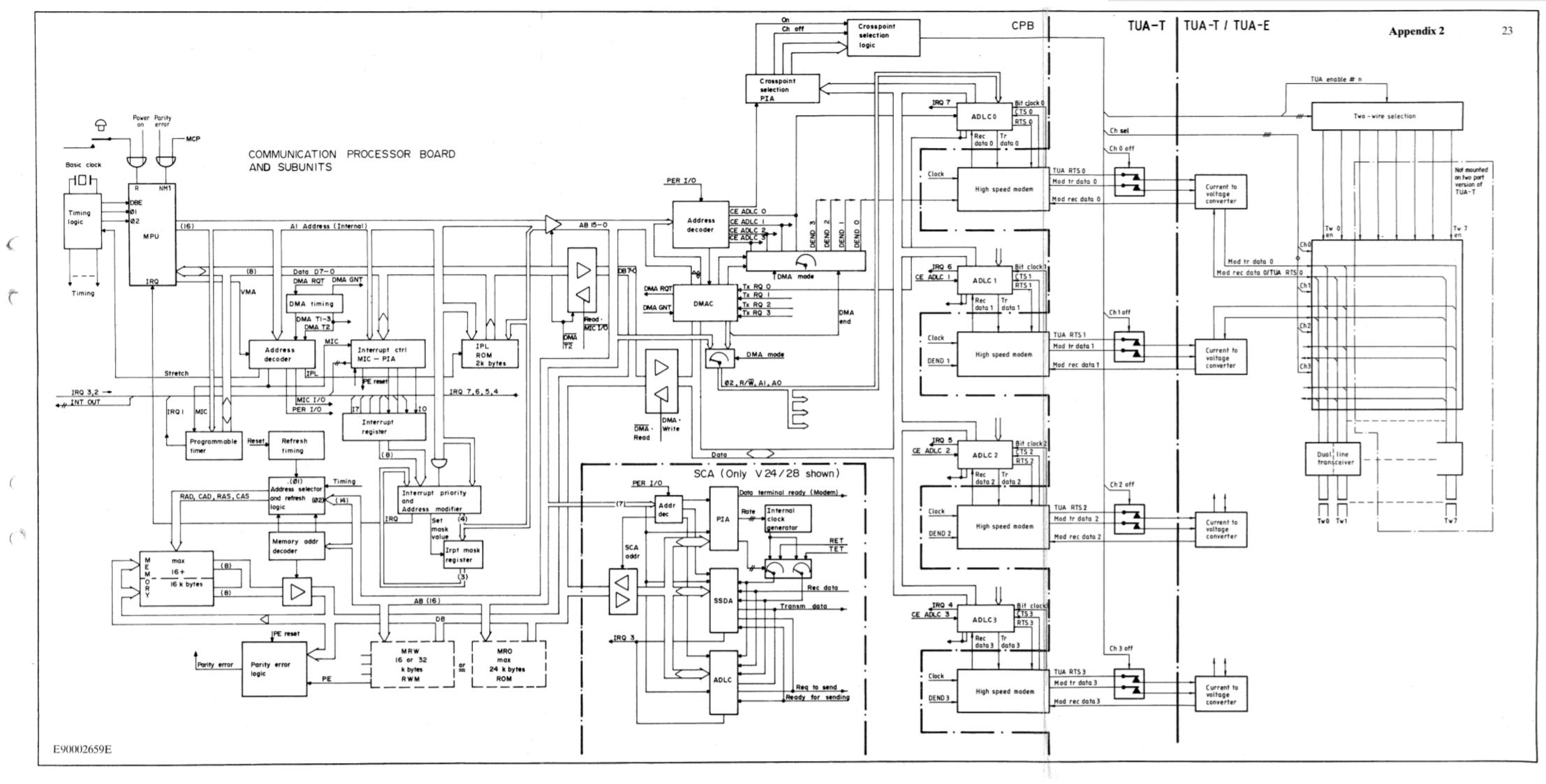

CPB = CP board

CPL = CP, local

CPR = CP, remote

CPS = CP power supply

CRU = Cathode ray tube unit

CTF = CP and terminal fan

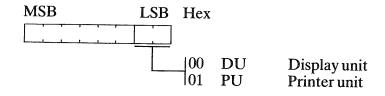

DPS = Display terminal power supplyDTC = Display terminal controller

DU = Display unit

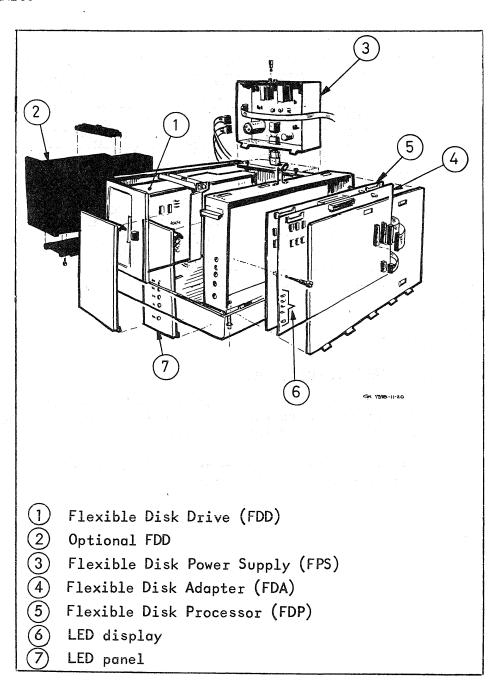

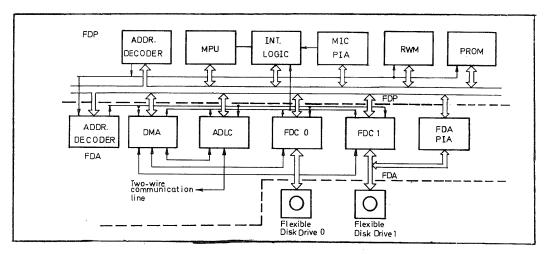

FD = Flexible disk unit

FDA = Flexible disk adapter

FDD = Flexible disk drive

FDP = Flexible disk processor

FPS = Flexible disk power supply

KB = Keyboard

KBC = Keyboard controller

KBU = Keyboardunit

KXB = Keyboard expansion board KXU = Keyboard expansion unit

MIA = MID adapter

MID = Magnetic identification device MRO = Memory board, RO memory MRW = Memory board, R/W memory

PTC = Printer terminal controller

PU = Printer unit

SCA = Synchronous communication adapter SCC = Synchronous communication controller

SPA = Selector pen adapter SPD = Selector pen device

TAB = TUA interconnection board TIA = Two-wire interface adapter TUA = Terminal unit adapter

UPS = Universal power supply

# Microcomputer

# Contents

| General  |                                                | 1  |

|----------|------------------------------------------------|----|

| Micropr  | ocessor Unit, MPU                              | 2  |

|          | MPU Registers                                  | 2  |

|          | MPU Signals                                    | 4  |

|          | Instruction Set and Addressing Modes           | 5  |

| Interrup | t Handling                                     | 8  |

| _        | General                                        | 8  |

|          | Address Modifier                               | 10 |

|          | Mask Register                                  | 10 |

|          | Interrupt Register                             | 10 |

|          | Generation and Direction of IRQs               | 10 |

|          | Interrupt Priority and Address modifier (FPLA) | 11 |

|          | Peripheral Interface Adapter, PIA              | 12 |

|          | Signals                                        | 12 |

|          | Registers                                      |    |

| Timing   |                                                | 16 |

|          | Basic Timing                                   | 16 |

|          | Bus Timing Example                             | 16 |

|          | Programmable Timer Module, PTM                 | 16 |

|          | Signals                                        | 18 |

|          | Registers                                      | 19 |

| Memory   | Organization and Access                        | 21 |

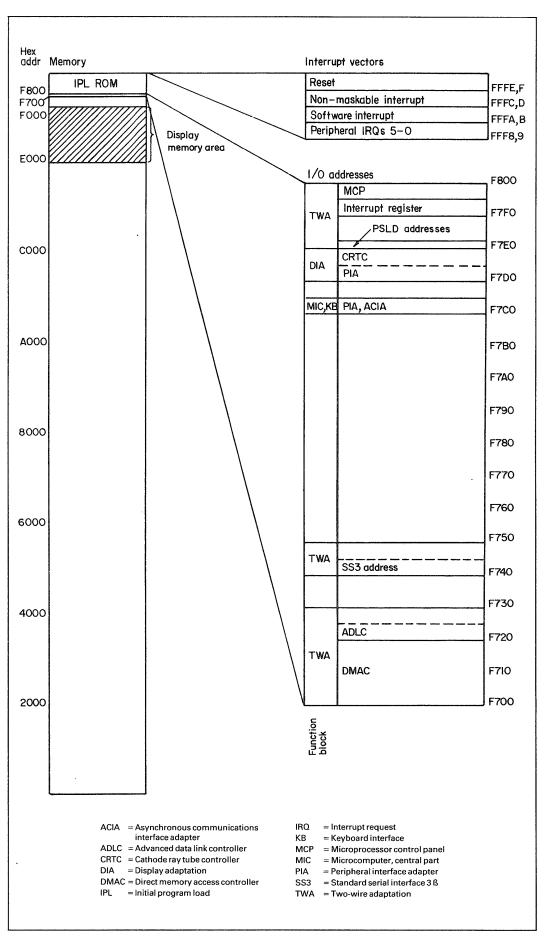

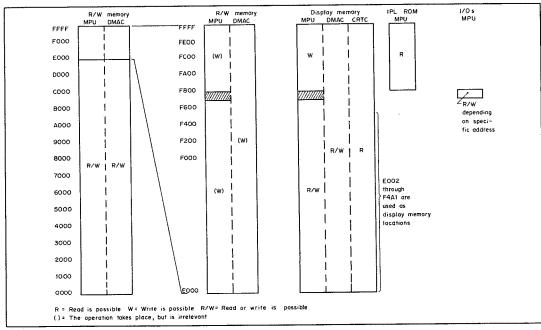

| -        | Memory Map                                     | 21 |

|          | Address Decoding and Direct Memory Access      | 23 |

|          | Address Decoder (FPLA)                         | 23 |

|          | Memory Access Multiplexing                     | 23 |

|          | Direct Memory Access                           | 24 |

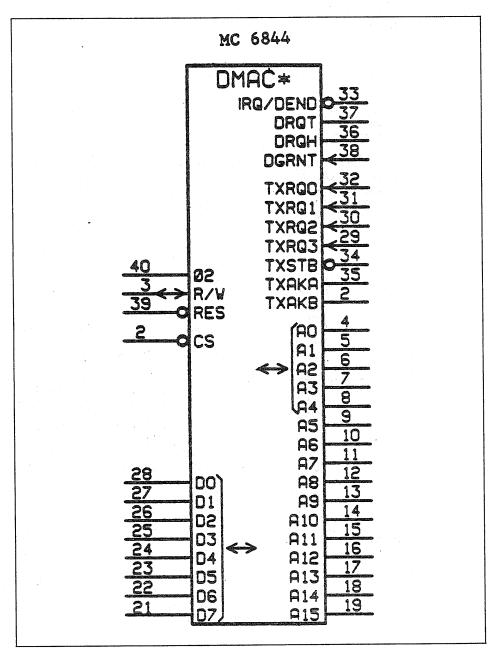

|          | Direct Memory Access Controller, DMAC          | 25 |

|          | DMAC Programming Example                       | 27 |

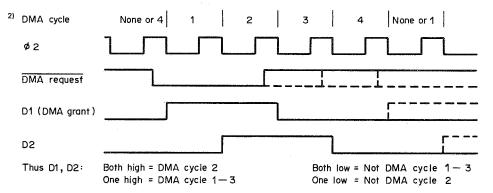

|          | DMA Timing                                     | 28 |

#### General

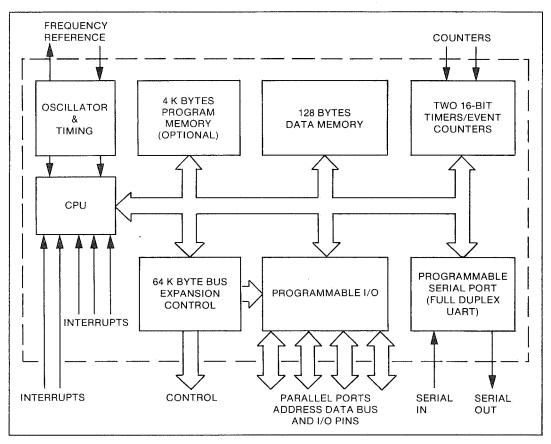

All main units of Alfaskop System 41 include a microcomputer. The purpose of this chapter is to describe the common attributes of the different M6800 family based microcomputers. Thus e.g. the most common LSI circuits of the M6800 family, the bus system, the addressing modes, the interrupt handling and the employed direct memory access method are described in this chapter. Even more detailed information on the M6800 family can be found in Motorola Semiconductors: Microcomputer components.

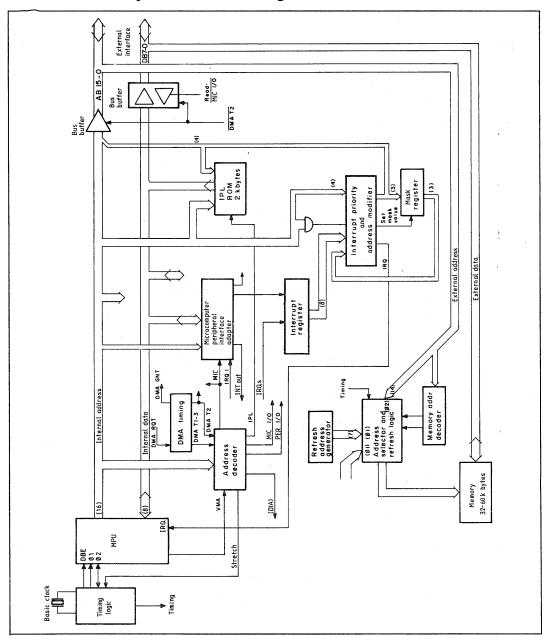

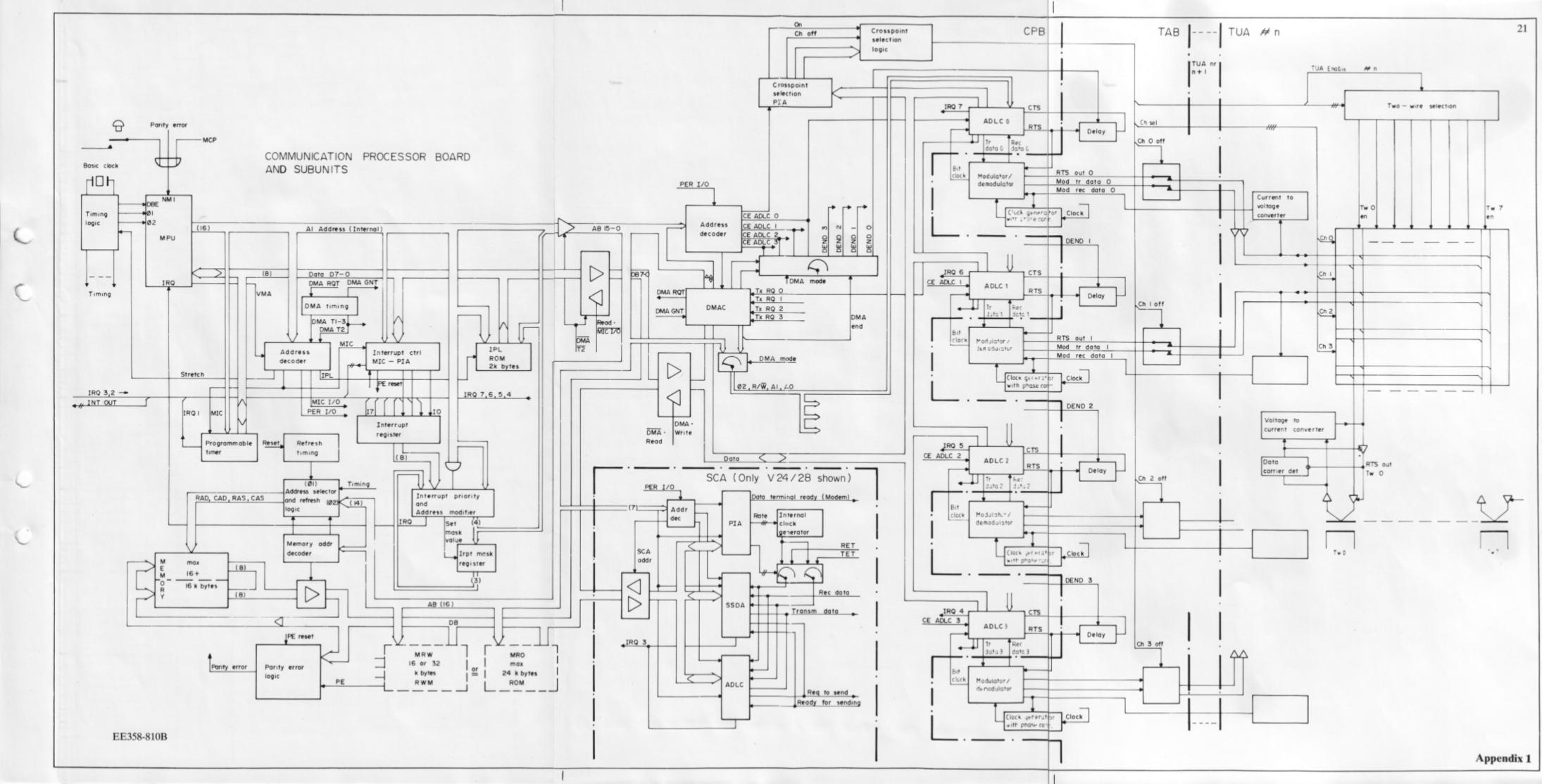

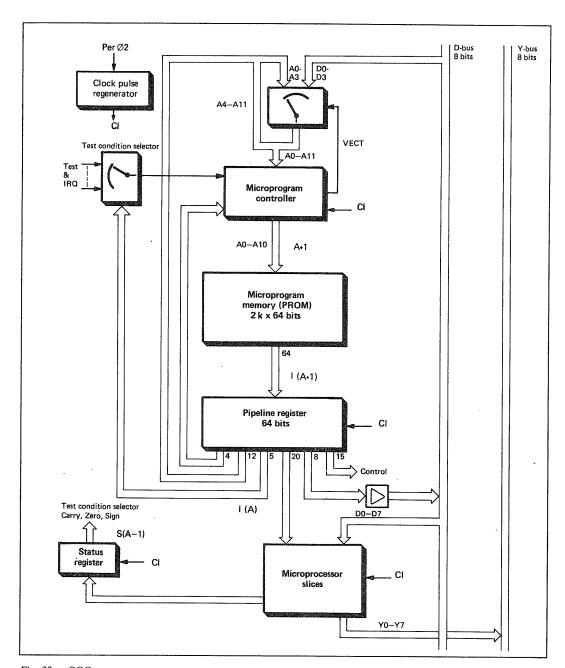

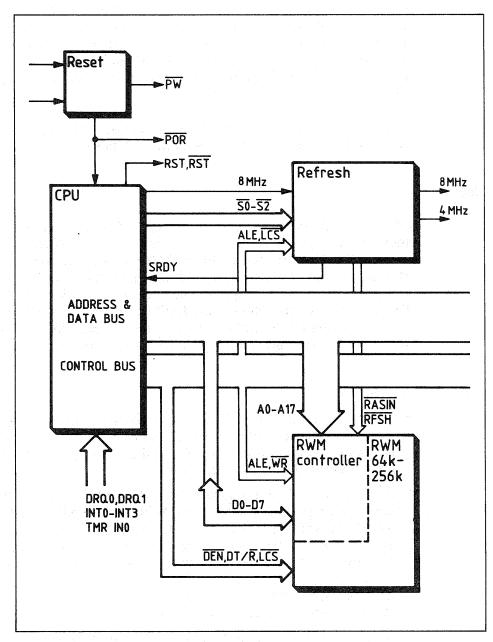

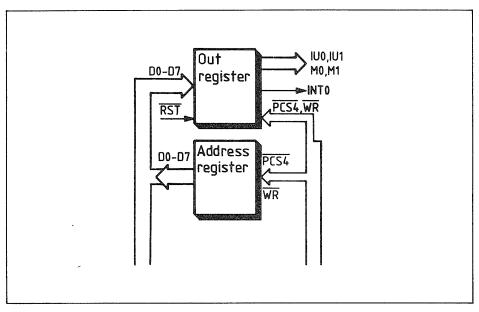

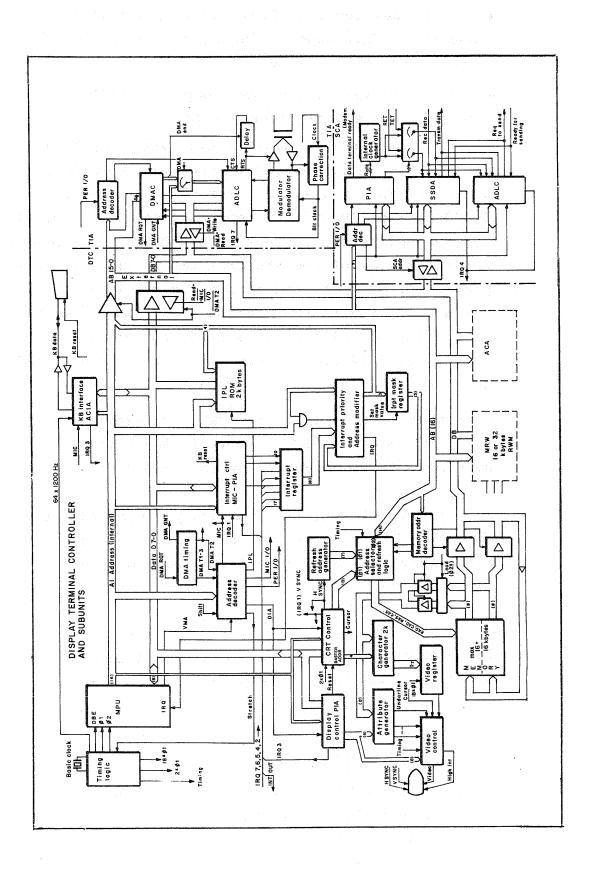

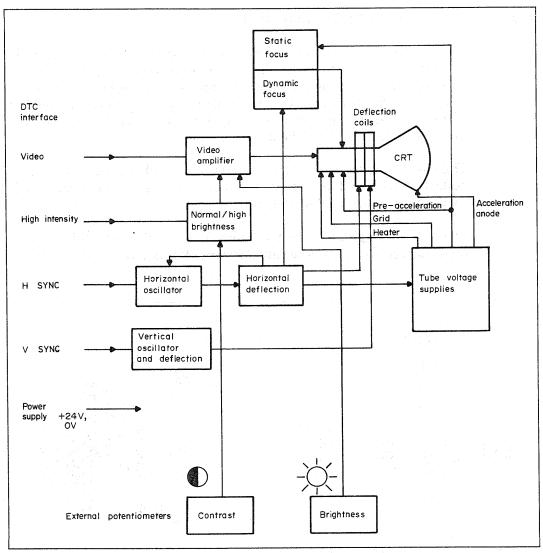

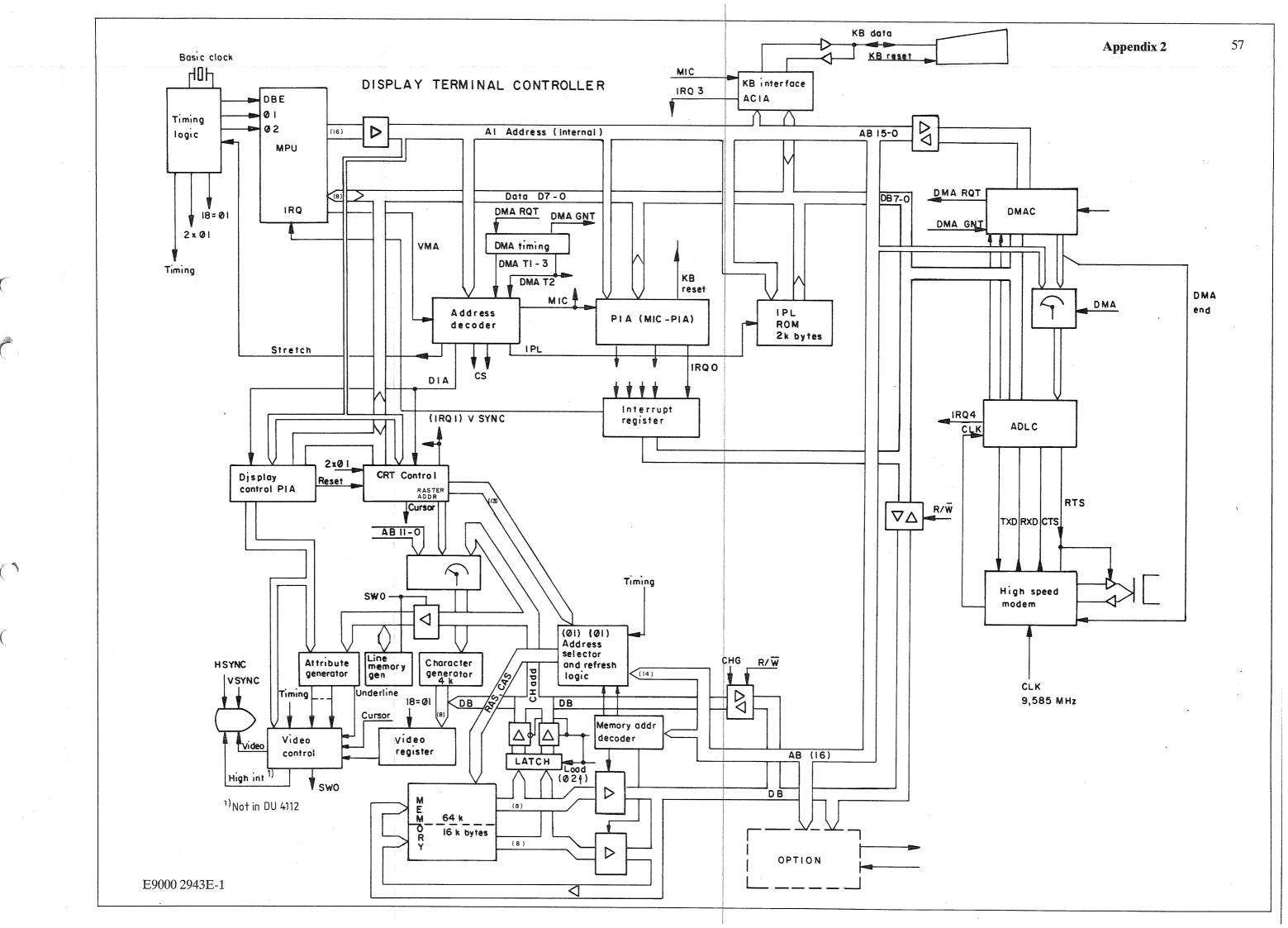

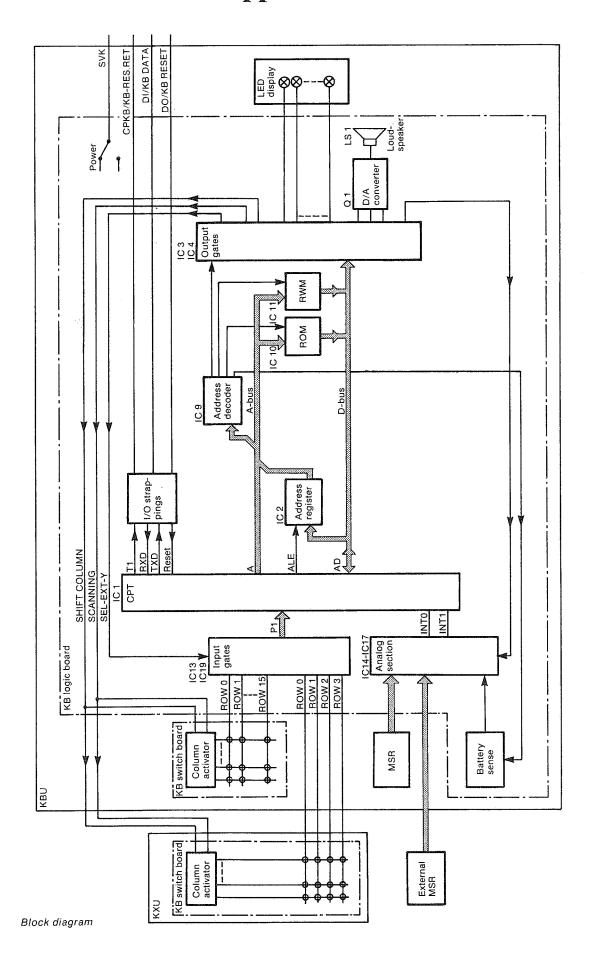

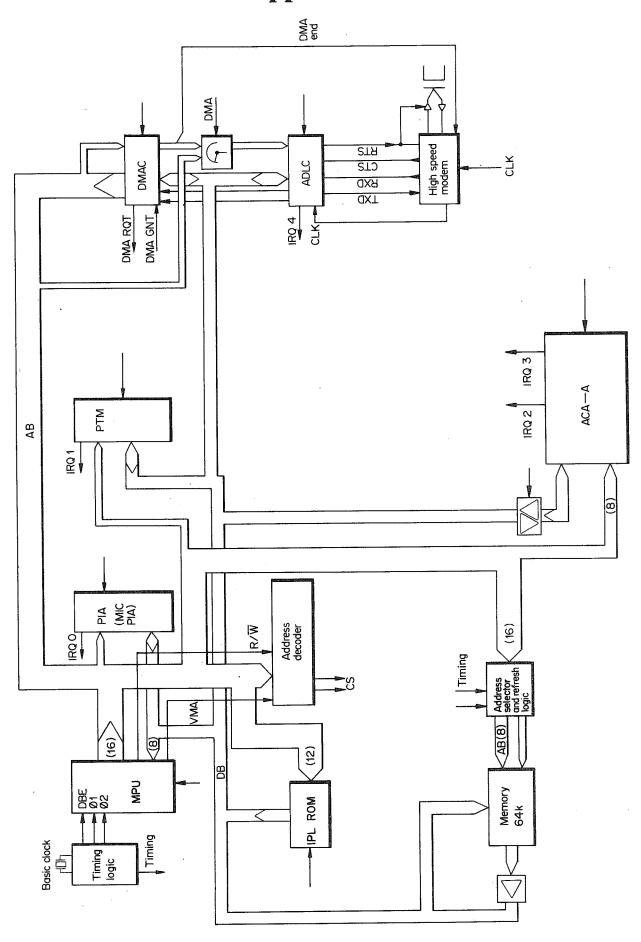

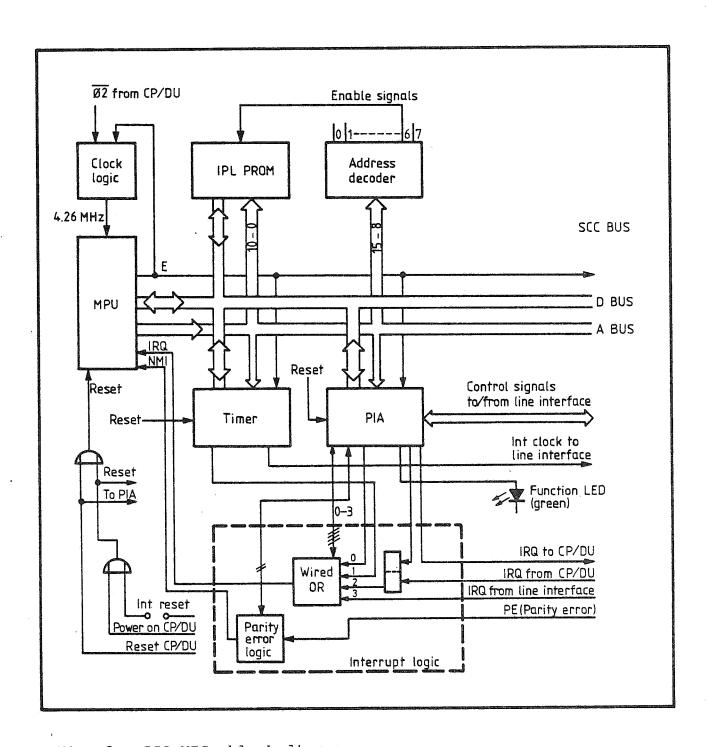

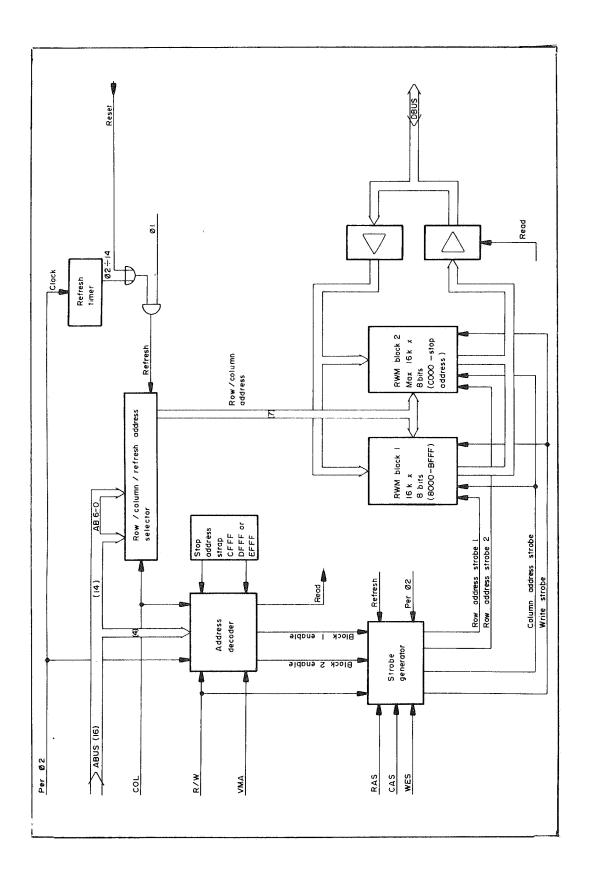

This chapter is directly applicable for the microcomputers in DU 4110, CPR 4101, CFU 4103, and in the communication processor parts of CPL 4102. (The reader ought also to be familiar with this chapter before studying the chapter on FD 4120.) The main functional blocks of the microcomputer are shown in Fig. 1.

Fig. 1. Microcomputer, basic block diagram

#### These are:

- Microprocessing unit, MPU

- Timing logic

- Memory

- Address decode, bus timing and parts of memory access multiplexing logic

- Interrupt control logic

- IPL ROM, i.e. a read only memory containing the necessary program for initial program loading

The microprocessing unit used is of the M6800 type or similar, thus with an 8-bit data bus and a 16-bit address bus. No specific I/O instructions are used, but registers of peripheral circuits like parallel interface and serial interface adapters are addressed just as memory locations. The MPU is described in detail below.

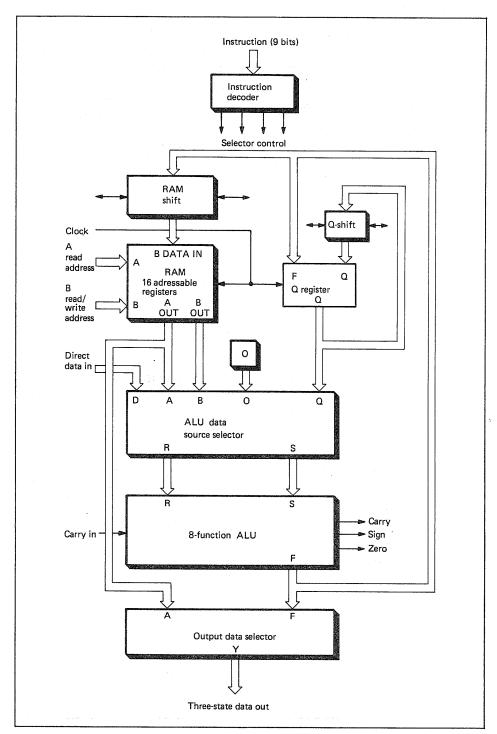

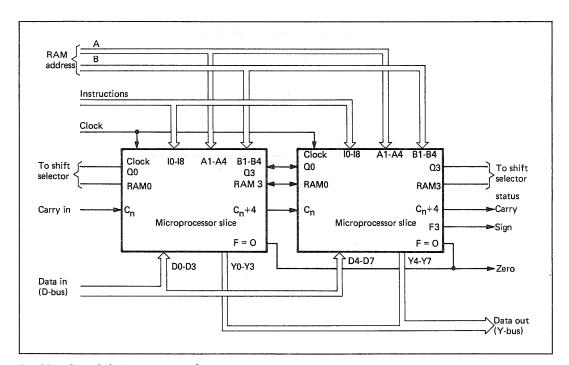

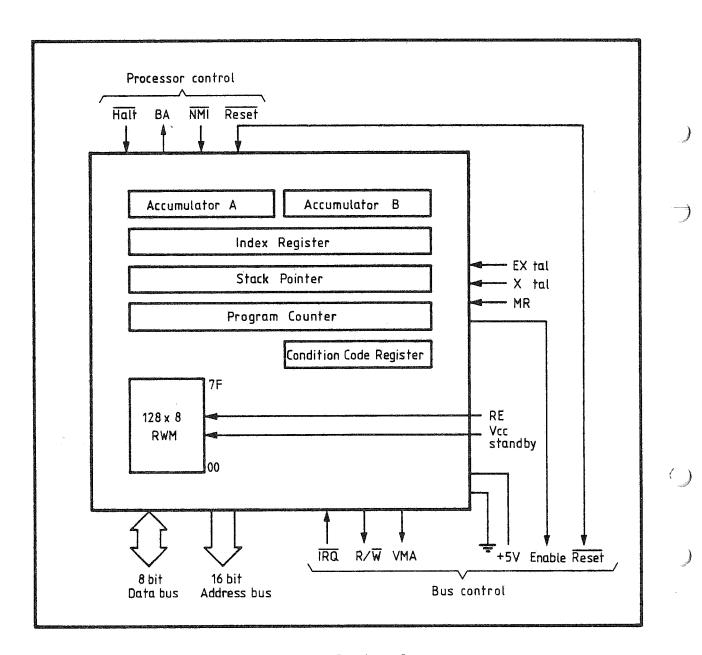

### Microprocessing Unit, MPU

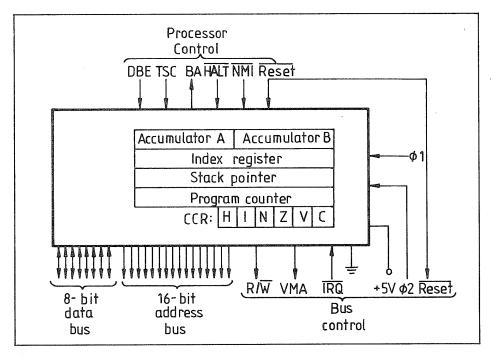

In this paragraph the hardware and software attributes of the MPU are dealt with. The MPU is an 8-bit parallel three-state device. It has 16 address bits and is thus capable of addressing 65,536 memory locations. See Fig. 2.

Fig. 2. MPU registers and signals

#### **MPU** Registers

Seen from the outside, the MPU contains six registers; three one byte registers and three double byte registers. The one byte registers are:

• Two accumulators named ACCA and ACCB used for storing operands for and results from operations.

- A condition code register, CCR, with 6 flag bits (b7 and b6 are always ones) signalling the result of a previous operation. The meaning of the different CCR bits, when set, are:

- b5 H A preceding operation (e.g. ADD, SUB, CMP) resulted in a half-carry from bit 3 to bit 4.

- 4 I When this bit is reset, the MPU will service a maskable interrupt request (IRQ). It will be set when an interrupt occurs, thus hindering or "masking" further interrupts (IRQs).

- 3 N The result of a preceding operation is negative (bit 7 of result = 1).

- 2 Z The result of a preceding operation = 0.

- 1 V A previous operation resulted in 2's complement overflow, i.e. a limit of the number area [- 128, 127] was passed.

- O C A carry from bit 7 was produced by a preceding operation or a borrow to bit 7 was needed to make the operation (SUB or CMP).

Detailed information on which CCR bits that are affected by a certain instruction is found in Fig. 4.

The 16-bit double registers, mostly used for addressing, are:

- Index register, which reduces program memory requirements as it can be loaded with a different memory address from the one contained in the program counter and stack pointer (see addressing modes below)

- Stack pointer, which should be initialized to point to the highest address of the read/write memory area to which the stack function has been assigned. At a Push data instruction (PSH) the contents of one of the accumulators (A or B) is stored in the stack and the stack pointer is automatically decremented. When data from the stack is wanted back to an accumulator a Pull data instruction (PUL) is used, resulting in an automatic incrementation of the stack pointer and a following loading of an accumulator from the memory cell pointed out by the stack pointer. The stack thus functions as a LIFO (last-in, first-out memory). The stack pointer is also automatically used at interrupts and at Jump to subroutine (JSR) and Branch to subroutine (BSR) instructions. In the interrupt case the contents of the MPU registers (but the stack pointer) are pushed into the stack and brought back at the Return from interrupt instruction (RTI). At JSR and BSR only the value of the program counter (i.e. the return address) is stacked away and brought back at the Return from subroutine instruction (RTS).

Both the index register and the stack pointer contents can be loaded from or stored into two consecutive memory cells using one instruction.

• Program counter. At reset and different interrupts, this counter is loaded with program addresses (interrupt vectors) stored at specific memory locations in the highest part of the memory area. The program counter is then automatically stepped through the program and also changed at jump or branch instructions. Otherwise it cannot be written or read.

#### **MPU Signals**

Apart from the 16 address bus lines and the 8 bidirectional data bus lines there are several other timing and control signals in the system. The clock inputs to the MPU are:

• Ø1 and Ø2, complementary, non-overlapping clocks. The cycle time mentioned in this text is the clock cycle time. During Ø1 high time the address is set up and during Ø2 high time data is set up and read or written. (On Ø2 going low.) See Timing paragraph for details.

Normal program execution can be stopped by four external signals, namely Interrupt request (IRQ), Non-maskable interrupt (NMI), Reset (R) and HALT.

- IRQ input being low will make the processor jump to an interrupt routine if the interrupt mask bit (I) in the MPU condition code register is reset.

- NMI input going low will always make the MPU jump to an interrupt routine after the present instruction has been completed.

- An incoming interrupt (IRQ, NMI or Software interrupt instruction) or Reset will set the I-bit to prevent further interrupts (IRQs) from interfering with the execution of the interrupt routine.

- Reset being low will make the processor stop (if it has started). When Reset goes high again the MPU will fetch the address of the restart routine from the two highest memory positions (FFFE<sub>(16)</sub> and FFFF<sub>(16)</sub>), load this address into the program counter and begin the restart sequence. The interrupt mask bit in the CCR will be set during Reset and must be cleared by the program if service of an IRQ is wanted.

- HALT being low will stop all program execution. Interrupts coming during HALT condition will be preserved and serviced after HALT has gone high again. If Reset is low during HALT condition, the restart routine will be entered when HALT goes high again. The MPU will signal that it is halted with a BA signal (see below).

- BA, Bus available, is high when the MPU is halted. BA is also high when the MPU is waiting for an interrupt as a result of a Wait for interrupt instruction. The address and the data bus as well as the R/W signal (see below) are then in high impedance state.

- R/W, Read/Write, signals the peripherals and memories whether the MPU is in read (high) or write (low) state. R/W is in high impedance state when the MPU is halted and its buses are available for another device (e.g. another MPU) to access the memories of the system (DMA, direct memory access).

- VMA, Valid memory address, is low or non-active during HALT. This

signal is active only during the cycles when the memory address from

the MPU should select a specific circuit.

- TSC, Three-state control, being high puts the R/W and address bus lines into high impedance state. The clocks for the MPU, Ø1 and Ø2, should be stopped to prevent false program execution. Ø1 should be held high.

- DBE, Data bus enable, which is generally tied to  $\emptyset$ 2, low, puts the data bus input/output in high impedance state (allowing DMA).

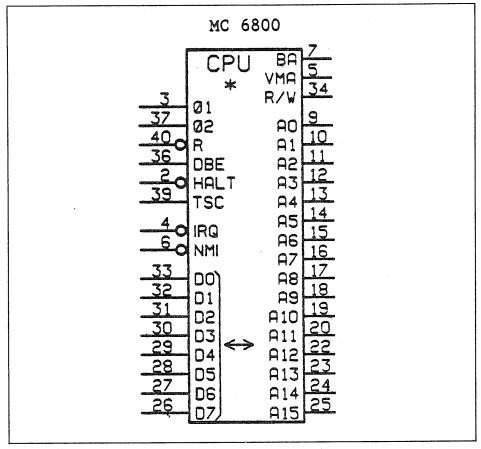

The drawing symbol is shown in Fig. 3.

Fig. 3. CPU drawing symbol

#### **Instruction Set and Addressing Modes**

The instruction set is shown in Fig. 4. The seven addressing modes mentioned in the headings of the instruction set are described below:

- Immediate addressing or zero-level addressing. In this case one operand is found in the memory cell (two cells for index register and stack manipulations) immediately following the operation code location.

- Direct and extended addressing or one-level addressing. In these modes the operand or the operation code of the next instruction at a jump instruction is found in the cell pointed out by the byte (for direct addressing) or 2 bytes (for extended addressing) following the operation code. Thus, with extended addressing it is possible to reach cells  $0000_{(16)}$  through FFFF<sub>(16)</sub> but with direct addressing only cells 0 through 255 in the memory map.

- Indexed addressing. In this case the effective address of the operand location is formed by adding an offset from 0 to 255 (contained in the second byte of the instruction) to the 16-bit address contained in the index register.

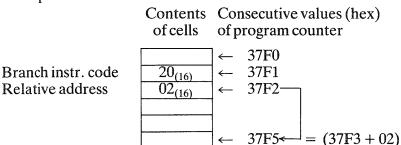

- Relative addressing. Here, the meaning of relative addressing (used for the branch instructions) is restricted to the case when the address to the next instruction is relative to the address of the cell following the two branch instruction bytes. Note that, as the relative address is expressed in 2's complement, it is a number between − 128 and + 127.

#### **ACCUMULATOR AND MEMORY INSTRUCTIONS**

|                               |             |    |     |   |     |      | AD  | DRES | SING | MO | DES   |     |     |     |      |    | BOOLEAN/ARITHMETIC OPERATION           | 100   | ND. | co  | DE   | RE       |

|-------------------------------|-------------|----|-----|---|-----|------|-----|------|------|----|-------|-----|-----|-----|------|----|----------------------------------------|-------|-----|-----|------|----------|

|                               |             |    | MME |   |     | IREC |     |      | NDE  | _  |       | XTN |     |     | PLIE |    | (All register labels                   | 5     |     | 3   |      | 1        |

| OPERATIONS                    | MNEMONIC    | OP | `   | = | OP  | -    | =   | OP   | `    | =  | OP    | _   | =   | OP  |      | == | refer to contents)                     | -     | 1   | N   | +    | ٧        |

| Add                           | ADDA        | 38 | 2   | 2 | 9B  | 3    | 2   | AB   | 5    | 2  | BB    | 4   | 3   |     |      |    | A+M -A                                 |       | •   |     |      |          |

| Add Acmitrs                   | ADDB<br>ABA | СВ | 2   | 2 | DB  | 3    | 2   | EB   | 5    | 2  | FB    | 4   | 3   | 18  | 2    | 1  | 8 + M - B ·<br>A + B - A               | 1 1   | 0   |     |      | :        |

| Add Acmitrs<br>Add with Carry | ADCA        | 89 | 2   | 2 | 99  | 3    | 2   | А9   | 5    | 2  | 89    | 4   | 3   | 18  | 2    | ŗ  |                                        |       |     | - 1 | - 1  | 1        |

| Add With Carry                | ADCB        | C9 | 2   | 2 | 09  | 3    | 2   | E9   | 5    | 2  | F9    | 4   | 3   |     |      |    | A + M + C - A<br>B + M + C - B         |       |     | - 1 |      | 1        |

| And                           | ANDA        | 84 | 2   | 2 | 94  | 3    | 2   | A4   | 5    | 2  | B4    | 4   | 3   |     |      |    | A·M·A                                  |       |     | ;   |      | R        |

| Milu                          | ANDB        | C4 | 2   | 2 | D4  | 3    | 2   | E4   | 5    | 2  | F4    | 4   | 3   |     |      |    | B-M ·B                                 | 1 1   | - 1 | il  |      | R        |

| Bit Test                      | BITA        | 85 | 2   | 2 | 95  | 3    | 2   | A5   | 5    | 2  | 85    | 4   | 3   |     |      |    | A M                                    | 1 (   | ı   | ٠,  |      | R        |

| Dit lest                      | BITB        | C5 | 2   | 2 | 05  | 3    | 2   | E5   | 5    | 2  | F5    | 4   | 3   |     |      |    | B·M                                    |       | - 1 | - 1 |      | R        |

| Clear                         | CLR         | "  | -   | - | 0.5 | ,    | -   | 6F   | 7    | 2  | 7F    | 6   | 3   |     |      |    | 00 · M                                 |       |     | . 1 |      | R        |

| on, ui                        | CLRA        |    |     |   |     |      |     | •    | •    | ٠  | l ''  | ٠   |     | 4F  | 2    | 1  | 00 · A                                 | 0     |     |     |      | R        |

|                               | CLRB        |    |     |   |     |      |     |      |      |    |       |     |     | 5F  | 2    | 1  | 00 · B                                 | 1 1   |     |     |      | R        |

| Compare                       | CMPA        | 81 | 2   | 2 | 91  | 3    | 2   | A1   | 5    | 2  | B1    | 4   | 3   | -   | _    |    | A M                                    | 1 1   |     |     |      | 1        |

| Compara                       | CMPB        | Cı | 2   | 2 | 01  | 3    | 2   | E1   | 5    | 2  | F1    | 4   | 3   |     |      |    | B - M                                  | 1 1   |     |     | - 1  | i        |

| Compare Acmitrs               | CBA         | -  | -   | _ |     | -    | _   |      | -    | -  |       |     |     | 11  | 2    | 1  | A B                                    | 1 1   |     |     | 1    |          |

| Complement, 1's               | COM         | l  |     |   |     |      |     | 63   | 7    | 2  | 73    | 6   | 3   |     | -    |    | M · M                                  | 1 1   |     |     |      | R        |

| ,                             | COMA        |    |     |   |     |      |     |      |      |    |       |     | - 1 | 43  | 2    | 1  | Ā·A                                    |       |     | - 1 |      | R        |

|                               | COMB        |    |     |   |     |      |     |      |      |    | ŀ     |     |     | 53  | 2    | 1  | B ⋅B                                   |       |     | - 1 |      | R        |

| Complement, 2's               | NEG         | ٠. |     |   |     |      |     | 60   | 7    | 2  | 70    | 6   | 3   |     | _    |    | 00 - M · M                             |       |     | . 1 |      | Dk       |

| (Negate)                      | NEGA        |    |     |   |     |      |     |      |      | -  | "     | •   | Ů   | 40  | 2    | 1  | 00 - A → A                             |       | - 1 |     |      | DIC      |

| (Trage Int                    | NEGB        |    |     |   |     |      |     |      |      |    |       |     |     | 50  | 2    | 1  | 00 - B · B                             | 1 1   |     |     |      | D        |

| Decimal Adjust, A             | DAA         |    |     |   |     |      |     |      |      |    |       |     |     | 19  | 2    | 1  | Converts Binary Add. of BCD Characters | 1 1   |     |     |      | 1        |

|                               |             | l  |     |   |     |      |     | ĺ    |      |    |       |     |     |     | -    |    | into BCD Format                        |       |     | .   | 1    | . [      |

| Decrement                     | DEC         | l  |     |   |     |      |     | 6A   | 7    | 2  | 7A    | 6   | 3   |     |      |    | M ~ 1 ~ M                              | •     |     | 1   | :    | 4        |

| o caramon.                    | DECA        | l  |     |   |     |      |     | •    |      | -  |       | •   | -   | 4A  | 2    | 1  | A - 1 - A                              |       | - 1 |     |      | 4        |

|                               | DECB        | 1  |     |   |     |      |     | ł    |      |    |       |     |     | 5A  | 2    | 1  | B - 1 - B                              |       |     | - 1 |      | 4        |

| Exclusive OR                  | EORA        | 88 | 2   | 2 | 98  | 3    | 2   | A8   | 5    | 2  | 88    | 4   | 3   | 0.1 | -    | •  | A⊕M → A                                | 0     |     | . 4 |      | R        |

| EXCIOSIVE O11                 | EORB        | C8 | 2   | 2 | D8  | 3    | 2   | E8   | 5    | 2  | F8    | 4   | 3   |     |      |    | B⊕M → B                                | 1 1   |     | . 1 |      | R        |

| Increment                     | INC         | ~  | -   |   | 50  | Ü    | -   | 6C   | 7    | 2  | 7C    | 6   | 3   |     |      |    | M + 1 - M                              | 1 1   |     |     |      | 5        |

| merement                      | INCA        | l  |     |   |     |      |     | "    | •    | -  | , ,   | ٠   | ٦   | 4 C | 2    | 1  | A + 1 - A                              | 1 1   |     |     |      | 3        |

|                               | INCB        |    |     |   |     |      |     | 1    |      |    |       |     |     | 5C  | 2    | i  | B+1 -B                                 | 1 1   |     |     |      | 3        |

| Load Acmitr                   | LDAA        | 86 | 2   | 2 | 96  | 3    | . 2 | A6   | 5    | 2  | В6    | 4   | 3   |     | -    | •  | M A                                    | 1 1   | - 1 |     |      | R        |

| Loud Million                  | LDAB        | C6 | 2   | 2 | D6  | 3    | 2   | E-6  | 5    | 2  | F.6   | 4   | 3   |     |      |    | M -B                                   |       |     |     |      | R        |

| Or, Inclusive                 | ORAA        | 8A | 2   | 2 | 9A  | 3    | 2   | AA   | 5    | 2  | BA.   | 4   | 3   |     |      |    | A + M → A                              |       |     | - 1 | - 1  | R        |

| OI, Inclusive                 | ORAB        | CA | 2   | 2 | DA  | 3    | 2   | EA   | 5    | 2  | FA    | 4   | 3   |     |      |    | B+M-B                                  |       |     |     |      | R .      |

| Push Data                     | PSHA        | "  | -   | 2 | 00  | 3    | -   | 1    | J    | ۲  | '^    | 7   | ٦   | 36  | 4    | 1  | A → MSP, SP - 1 → SP                   | 1 1   |     |     | - 1  | 0        |

| Cost Data                     | PSHB        |    |     |   |     |      |     |      |      |    |       |     |     | 37  | 4    | i  | B MSP, SP 1 SP                         |       |     | - 1 |      | •        |

| Pull Data                     | PULA        |    |     |   |     |      |     |      |      |    | ŀ     |     |     | 32  | 4    | i  | SP + 1 - SP, M <sub>SP</sub> → A       | 1 . 1 |     |     | 1    | ٠        |

|                               | PULB        |    |     |   |     |      |     |      |      |    |       |     |     | 33  | 4    | i  | SP + 1 SP, MSP B                       | 1 1   |     | - 1 | 1    |          |

| Rotate Left                   | ROL         |    |     |   |     |      |     | 69   | 7    | 2  | 79    | 6   | 3   | 00  |      |    | M)                                     |       | - 1 | - 1 | - 1  | 6        |

| HOIGIG EGIT                   | ROLA        |    |     |   |     |      |     | "    | •    | -  | '*    | ٠   | ١   | 49  | 2    | 1  | A}                                     |       |     |     |      | <u></u>  |

|                               | ROLB        |    |     |   |     |      |     |      |      |    |       |     |     | 59  | 2    | i  | B C b7 b0                              |       |     |     |      | 6        |

| Rotate Right                  | ROR         |    |     |   | 1   |      |     | 66   | 7    | 2  | 76    | 6   | 3   | 00  | -    | •  | m)                                     |       | - 1 |     |      | <u>6</u> |

| morare mgot                   | RORA        | 1  |     |   |     |      |     | "    | •    | -  | ,,,   | ٠   | ١,  | 46  | 2    | 1  | A} -0 - cccccc                         |       |     |     |      | 6        |

|                               | RORB        |    |     |   |     |      |     |      |      |    |       |     | - 1 | 56  | 2    | i  | B C b7 - b0                            |       |     | - 1 |      | ŏ        |

| Shift Left, Arithmetic        | ASL         | 1  |     |   |     |      |     | 68   | 7    | 2  | 78    | 6   | 3   | ••• | -    |    | - (M                                   |       |     |     |      | <u></u>  |

| oint cert, Artificite         | ASLA        |    |     |   |     |      |     | "    | ,    | -  | , , , | ٠   | ٦   | 48  | 2    | 1  |                                        |       |     | - 1 |      | <u></u>  |

|                               | ASLB        |    |     |   |     |      |     |      |      |    |       |     |     | 58  | 2    | i  | A C b7 b0                              |       |     | - 1 |      | <u></u>  |

| Shift Right, Arithmetic       | ASR         | 1  |     |   |     |      |     | 6/   | 7    | 2  | 77    | 6   | 3   | 30  | -    | '  | M)                                     | 1 1   |     | - 1 |      | <u></u>  |

| Sint right, Arthmetic         | ASRA        |    |     |   |     |      |     | "    | '    | -  | l ''  | v   | ٦   | 47  | 2    | 1  |                                        |       |     |     |      |          |

|                               | ASRB        | İ  |     |   |     |      |     |      |      |    |       |     |     | 57  | 2    | i  | A }                                    |       |     | 1   | . 1. | 6        |

| Chife Diahe Lauin             |             |    |     |   |     |      |     | 64   | 7    | 2  | 74    | c   | 2   | 37  | 2    | •  | " (                                    | 1 1   | 1   |     |      |          |

| Shift Right, Logic            | LSR         |    |     |   |     |      |     | 04   | 7    | 2  | 74    | 6   | 3   |     |      |    | M                                      |       |     | R   |      | 9        |

|                               | LSRA        | 1  |     |   |     |      |     | l    |      |    |       |     | j   | 44  | 2    | 1  | A 0                                    | •     |     |     |      | 9        |

| Can Ala-                      | LSRB        | 1  |     |   | 97  | ,    | ,   |      | c    | •  | ٦,    | r   | ٦   | 54  | 2    | 1  | ( 0 )                                  | 0     |     |     |      | <u></u>  |

| Store Açmitr.                 | STAA        | 1  |     |   |     | 4    | 2   | A7   | 6    | 2  | 87    | 5   | 3   |     |      |    | A M                                    | 0     |     | ٠.  |      | R        |

|                               | STAB        |    | _   | _ | 07  | 4    | 2   | E7   | 6    | 2  | F7    | 5   | 3   |     |      |    | B · M                                  | 6     | - 1 |     |      | R        |

| Subtract                      | SUBA        | 80 | 2   | 2 | 90  | 3    | 2   | A0   | 5    | 2  | 80    | 4   | 3   |     |      |    | A ~ M - A                              | 0     | į.  | 1   |      | 1        |

|                               | SUBB        | CO | 2   | 2 | DO  | 3    | 2   | EO   | 5    | 2  | F0    | 4   | 3   |     | _    |    | B - M - B                              | 9     |     | . 1 | . 1  | 1        |

| Subtract Acmitrs.             | SBA         |    | _   | _ |     |      | _   | ١    | -    | _  |       |     |     | 10  | 2    | 1  | A - B - A                              | •     | •   | 1   |      | 1        |

| Subtr. with Carry             | SBCA        | 82 | 2   | 2 | 92  | 3    | 2   | A2   | 5    | 2  | B2    | 4   | 3   |     |      |    | A~M~C→A                                | 9     | •   | 1   | - 1  | 1        |

|                               | SBCB        | C2 | 2   | 2 | D2  | 3    | 2   | E2   | 5    | 2  | F2    | 4   | 3   |     |      |    | B - M - C - B                          | •     | •   | 1   | 1    | 1        |

| Transfer Acmitrs              | TAB         |    |     |   |     |      |     |      |      |    |       |     |     | 16  | 2    | 1  | A ~ B                                  | •     | •   | !   |      | R        |

|                               | TBA         |    |     |   |     |      |     |      |      |    |       |     |     | 17  | 2    | 1  | B ·-A                                  |       | •   | 1   |      | R        |

| Test, Zero or Minus           | TST         |    |     |   |     |      |     | 60   | 7    | 2  | 70    | 6   | 3   |     |      |    | M - 00                                 |       |     | 1   |      | В        |

|                               | TSTA        |    |     |   |     |      |     |      |      |    |       |     |     | 4D  | 2    | 1  | A - 00                                 | 0     |     | . 1 |      | R        |

|                               | TSTB        |    |     |   |     |      |     |      |      |    |       |     |     | 5D  | 2    | 1  | B ~ 00                                 | 0     |     | !   | 1    | R        |

|                               |             |    |     |   |     |      |     | Ь    |      |    | L     |     |     |     |      |    | L                                      | н     |     | +   | z    |          |

#### LEGEND:

- OP Operation Code (Hexadecimal);

Number of MPU Cycles;

- Number of Program Bytes;

- Arithmetic Plus; Arithmetic Minus;

- Boolean Inclusive OR; Boolean Exclusive OR; Complement of M;

- **.**

- Transfer Into; Bit = Zero;

- 00 Byte = Zero;

- Boolean AND;

MSP Contents of memory location pointed to be Stack Pointer;

Note - Accumulator addressing mode instructions are included in the column for IMPLIED addressing

#### CONDITION CODE SYMBOLS:

- Half-carry from bit 3; Interrupt mask

- Negative (sign bit) Zero (byte)

- Overflow, 2's complement Carry from bit 7

- Reset Always

- Set Always

Test and set if true, cleared otherwise

- Not Affected

MOTOROLA Semiconductor Products Inc.

#### INDEX REGISTER AND STACK MANIPULATION INSTRUCTIONS

|                       |          |      |     |   |    |      |      |    |     |     |    |     |   |    |       |     |                                                   | CO | ND | ı. CC | )DE | R   | EG. |

|-----------------------|----------|------|-----|---|----|------|------|----|-----|-----|----|-----|---|----|-------|-----|---------------------------------------------------|----|----|-------|-----|-----|-----|

|                       |          | - 11 | мме | D | D  | IREC | CT . | -1 | NDE | X · | Ε  | XTN | D | IA | 1PLII | ED  | ]                                                 | 5  | 4  | 3     | 2   | 1   | 0   |

| POINTER OPERATIONS    | MNEMONIC | OP   | ~   | # | OP | ~    | =    | OP | ~   | =   | OP | ~   | = | OP | ~     | =   | BOOLEAN/ARITHMETIC OPERATION                      | Н  | 1  | N     | z   | ٧   | C   |

| Compare Index Reg     | CPX      | 80   | 3   | 3 | 90 | 4    | 2    | AC | 6   | 2   | ВÇ | 5   | 3 |    |       |     | XH - M, XL - (M + 1)                              |    |    | 1     | :   | (8) | •   |

| Decrement Index Reg   | DEX      |      |     | 1 |    |      |      |    | ļ   |     | 1  |     |   | 09 | 4     | 1   | X − 1 → X                                         |    | •  |       | 1:  |     | •   |

| Decrement Stack Pntr  | DES      |      |     |   |    |      |      |    |     |     |    | i   |   | 34 | 4     | 1   | SP − 1 → SP                                       |    |    |       |     | 0   | •   |

| Increment Index Reg   | INX      |      |     |   |    |      | l    |    | 1   |     |    |     |   | 08 | 4     | 1 . | X + 1 → X                                         |    |    |       | i   | •   |     |

| Increment Stack Potr  | INS      |      |     |   |    |      | l    | 1  |     |     |    |     |   | 31 | 4     | 1   | SP + 1 → SP                                       |    | •  |       |     |     |     |

| Load Index Reg        | LDX      | CE   | 3   | 3 | DE | 4    | 2    | EE | 6   | 2   | FE | 5   | 3 |    |       |     | M → XH, (M + 1) -+ XL                             |    |    | 9     | [1] | R   | •   |

| Load Stack Pntr       | LDS      | 8E   | 3   | 3 | 9E | 4    | 2    | AE | 6   | 2   | BE | 5   | 3 |    |       | ]   | $M \rightarrow SP_{H_1}(M+1) \rightarrow SP_L$    |    |    | 9     | :   | R   | • ] |

| Store Index Reg       | STX      |      |     |   | DF | 5    | 2    | EF | 7   | 2   | FF | 6   | 3 |    |       |     | $X_H \rightarrow M, X_L \rightarrow (M+1)$        |    |    | 9     | :   | R   | •   |

| Store Stack Pntr      | STS      |      | l   |   | 9F | 5    | 2    | AF | 7   | 2   | BF | 6   | 3 |    |       |     | $SP_H \rightarrow M$ , $SP_L \rightarrow (M + 1)$ |    |    | 9     | :   | R   | •   |

| Indx Reg → Stack Pntr | TXS      |      |     |   |    |      |      |    |     |     |    |     |   | 35 | 4     | 1   | X - 1 → SP                                        |    |    | •     | •   | •   | • ; |

| Stack Pntr → Indx Reg | TSX      |      |     |   |    |      |      |    | 1   |     |    |     |   | 30 | 4     | 1   | SP + 1 - X                                        |    | 9  |       | 9   |     | •   |

#### JUMP AND BRANCH INSTRUCTIONS

|                          |          | RE | LATI | VE | - 11 | NDE | K | E  | XTN | D | IM | PLIE | D  |                                       | 5 | 4 | 3   | 2       | 1   |   |

|--------------------------|----------|----|------|----|------|-----|---|----|-----|---|----|------|----|---------------------------------------|---|---|-----|---------|-----|---|

| OPERATIONS               | MNEMONIC | OP | ~    | #  | OP   | ۲   | # | OP | ~   | # | OP | ~    | #  | BRANCH TEST                           | Н | 1 | N   | Z       | ٧   |   |

| Branch Always            | BRA      | 20 | 4    | 2  |      |     | 7 |    |     |   |    |      |    | None                                  |   |   | 9   |         |     | T |

| Branch If Carry Clear    | BCC      | 24 | 4    | 2  |      |     |   |    |     |   |    |      |    | C = 0                                 |   |   |     |         | •   | ١ |

| Branch If Carry Set      | BCS      | 25 | 4    | 2  |      |     |   |    | 1.0 |   |    |      |    | C = 1                                 |   |   |     |         |     |   |

| Branch If = Zero         | BEQ      | 27 | 4    | 2  |      |     |   |    |     |   |    |      |    | Z = 1                                 |   | • |     |         | 9   | 1 |

| Branch If ≥ Zero         | BGE      | 2C | 4    | 2  |      |     |   |    |     | 1 |    |      |    | N ⊕ V = 0                             |   | • |     |         |     | 1 |

| Branch If > Zero         | BGT      | 2E | 4    | 2  |      |     |   |    |     |   |    |      |    | Z + (N ⊕ V) = 0                       |   | • |     |         |     | 1 |

| Branch If Higher         | BHI      | 22 | 4    | 2  |      |     |   |    |     |   |    |      |    | C + Z = 0                             |   |   |     |         |     | ļ |

| Branch If ≤ Zero         | BLE      | 2F | 4    | 2  |      |     |   |    |     |   | l  |      |    | Z+(N + V) = 1                         |   |   |     |         |     |   |

| Branch If Lower Or Same  | BLS      | 23 | 4    | 2  |      |     |   |    |     |   |    |      |    | C + Z = 1                             |   |   |     |         |     |   |

| Branch If < Zero         | BLT      | 2D | 4    | 2  |      |     |   |    |     |   |    |      |    | N ⊕ V ≈ 1                             |   |   |     |         |     | - |

| Branch If Minus          | BMI      | 2B | 4    | 2  |      |     |   |    |     |   |    |      | Ì. | N = 1                                 |   |   |     |         |     | ı |

| Branch If Not Equal Zero | BNE      | 26 | 4    | 2  |      |     |   |    |     |   | l  |      |    | Z = 0                                 |   |   |     |         |     | - |

| Branch If Overflow Clear | BVC      | 28 | 4    | 2  |      |     |   |    |     |   |    |      |    | V = 0                                 |   |   |     |         |     | 1 |

| Branch If Overflow Set   | BVS      | 29 | 4    | 2  |      |     |   |    |     |   |    |      |    | V = 1                                 |   |   |     |         |     |   |

| Branch If Plus           | BPL      | 2A | 4    | 2  |      |     |   |    |     |   | ì  |      |    | N = 0                                 |   |   |     |         |     |   |

| Branch To Subroutine     | BSR      | 80 | 8    | 2  |      |     |   |    |     |   |    |      |    |                                       |   |   |     |         |     | 1 |

| Jump                     | JMP      | 1  |      |    | 6E   | 4   | 2 | 7E | 3   | 3 |    |      |    |                                       |   |   |     |         |     | 1 |

| Jump To Subroutine       | JSR      | 1  |      | 1  | AD   | 8   | 2 | BD | 9   | 3 |    |      |    |                                       |   |   |     |         |     | ١ |

| No Operation             | NOP      | 1  | 1    |    |      |     |   |    |     |   | 01 | 2    | 1  | Advances Prog. Cntr. Only             |   |   |     |         |     | - |

| Return From Interrupt    | RTI      | İ  |      |    |      |     |   |    |     |   | 3B | 10   | 1  | · · · · · · · · · · · · · · · · · · · |   | 1 | - 6 | <u></u> | 1 - | • |

| Return From Subroutine   | RTS .    |    |      |    |      |     |   |    |     |   | 39 | 5    | 1  |                                       |   |   | ۱ . | 1 0     |     | 1 |

| Software Interrupt       | SWI      |    |      |    |      |     |   |    |     |   | 3F | 12   | 1  |                                       |   |   |     |         |     | 1 |

| Wait for Interrupt *     | WAI      |    |      |    | 1    |     |   |    |     |   | 3E | 9    | 1  |                                       |   | m | I - |         |     | ı |

#### CONDITION CODE REGISTER MANIPULATION INSTRUCTIONS

|                      |          |    |       |   |                   |     | CUN | D. CE | INF | REG | • |   |

|----------------------|----------|----|-------|---|-------------------|-----|-----|-------|-----|-----|---|---|

|                      |          | IN | IPLIE | D |                   | 5   | 4   | 3     | 2   | 1   | 0 |   |

| OPERATIONS           | MNEMONIC | OP | ~     | = | BOOLEAN OPERATION | Н   | 1   | N     | Z   | ν   | C |   |

| Clear Carry          | CLC      | 0C | 2     | 1 | 0 → C             |     |     | •     |     | •   | R | - |

| Clear Interrupt Mask | CLI      | 0E | 2     | 1 | 0 → 1             |     | R   |       |     |     |   | 1 |

| Clear Overflow       | CLV      | 0A | 2     | 1 | 0 → V             |     | •   | •     |     | R   |   |   |

| Set Carry            | SEC      | 00 | 2     | 1 | 1 → C             | •   |     |       |     | •   | S | 1 |

| Set Interrupt Mask   | SEI      | 0F | 2     | 1 | 1 → 1             |     | s   |       | •   | •   | • | ı |

| Set Overflow         | SEV      | 0B | 2     | 1 | 1 → V             |     |     | 0     |     | S   |   | Ŀ |

| Acmltr A → CCR       | TAP      | 06 | 2     | 1 | A → CCR           | l — |     | (1    | 2)  |     | — | 1 |

| CCR → Acmitr A       | TPA      | 07 | 2     | 1 | CCR → A           |     |     |       |     |     |   | l |

CONDITION CODE REGISTER NOTES: (Bit set if test is true and cleared otherwise)

| 1 | (Bit V) | Test: Result = 10000000?                                                 | 7  | (Bit N) | Test: Sign bit of most significant (MS) byte = 1?                 |

|---|---------|--------------------------------------------------------------------------|----|---------|-------------------------------------------------------------------|

| 2 | (Bit C) | Test: Result = 00000000?                                                 | 8  | (Bit V) | Test: 2's complement overflow from subtraction of MS bytes?       |

| 3 | (Bit C) | Test: Decimal value of most significant BCD Character greater than nine? | 9  | (Bit N) | Test: Result less than zero? (Bit 15 = 1)                         |

|   |         | (Not cleared if previously set.)                                         | 10 | (All)   | Load Condition Code Register from Stack. (See Special Operations) |

| 4 | (Bit V) | Test: Operand = 10000000 prior to execution?                             | 11 | (Bit I) | Set when interrupt occurs. If previously set, a Non-Maskable      |

| 5 | (Bit V) | Test: Operand = 01111111 prior to execution?                             |    |         | Interrupt is required to exit the wait state.                     |

| 6 | (Bit V) | Test: Set equal to result of N⊕C after shift has occurred.               | 12 | (AII)   | Set according to the contents of Accumulator A.                   |

MOTOROLA Semiconductor Products Inc.

Fig. 4b Instruction set

Example:

• Implied and accumulator addressing. The instructions using these addressing modes are one byte instructions, where the operand or operands are understood from or contained in the operation code. Mostly these are instructions affecting only one or two MPU registers. For the Push data (PSH), Pull data (PUL), return (RTI, RTS), Software interrupt (SWI), and Wait for interrupt (WAI) instructions, however, memory locations indicated by the stack pointer are also affected. The No operation (NOP) instruction is special in that it only advances the program counter one step and introduces a delay of two MPU cycles before active program execution is resumed.

### **Interrupt Handling**

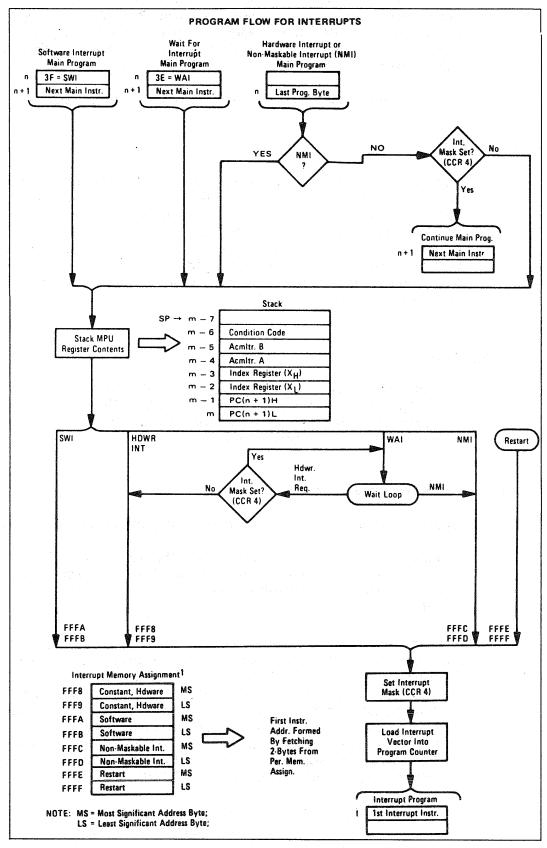

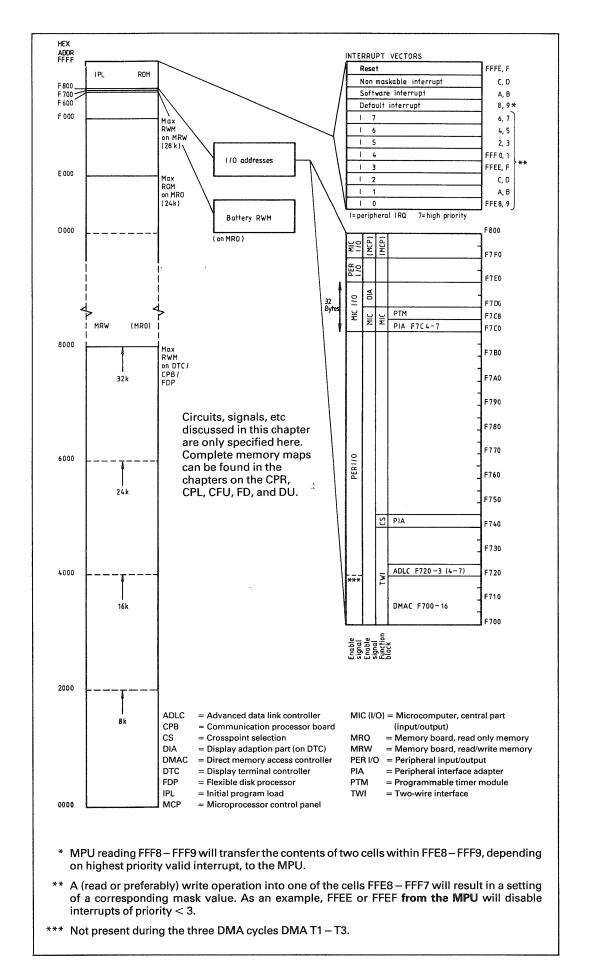

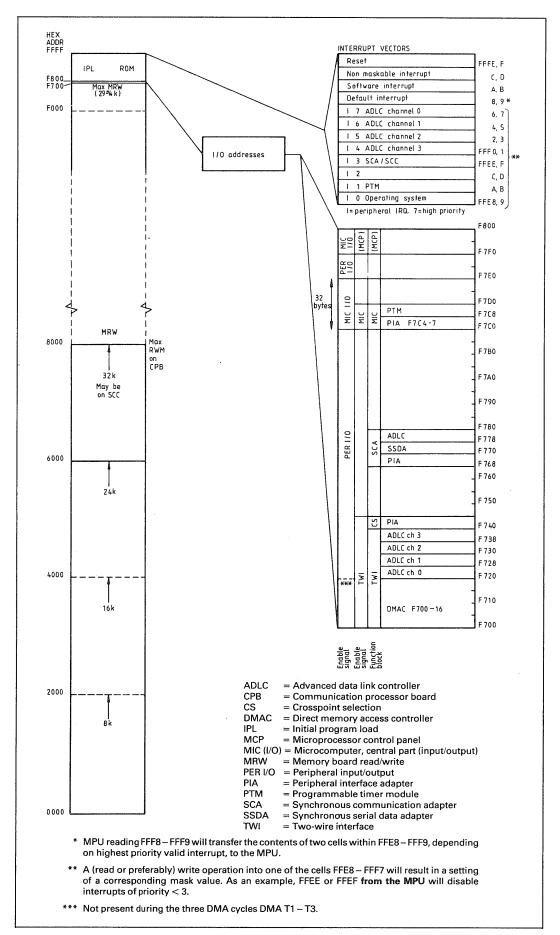

Please refer to Fig. 1.

#### General

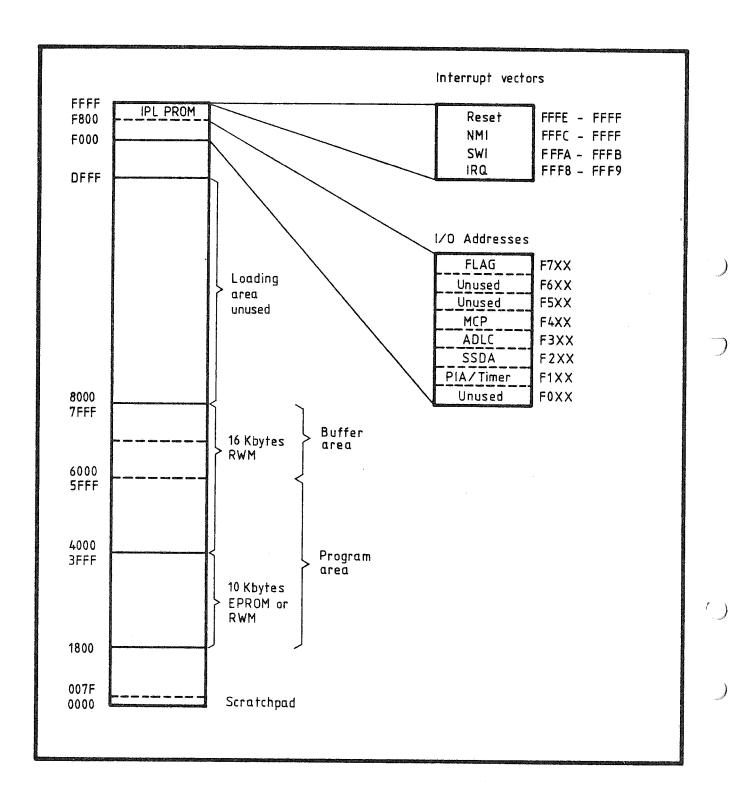

The MPU only reacts to four interrupts (Reset, Non-maskable interrupt, Software interrupt and Interrupt request, see Fig. 5). More interrupts are wanted and an interrupt logic is therefore contained in the microcomputer. This logic permits eight interrupts to use the IRQ line to the MPU.

In addition to the possibility to mask all IRQs by setting the I-bit of the MPU condition code register (CCR), the MPU can set a value between 0 and 7 in a mask register to prevent IRQs below the handeled level from interrupting the program execution. IRQ 7 is the highest priority interrupt and IRQ 0 the lowest. Thus, if e.g. the mask register is set to 5, only interrupts on level 5, 6 or 7 will activate the IRQ line to the MPU.

The MPU reacts to an IRQ (if the I-bit is reset) by:

- Completing the execution of the present instruction and stepping the program counter to point to the next instruction

- Saving the contents of its registers in the stack (contents of program counter = return address, etc)

- Trying to fetch the address to the interrupt routine from the memory cells FFF8<sub>(16)</sub> and FFF9<sub>(16)</sub>

- Setting the interrupt mask bit of the CCR to disable further IRQs.

When returning from an interrupt routine (by the RTI instruction) the registers of the MPU get their old contents back from the stack. Thus the execution of the interrupted program is resumed. Note that the I-bit value is 0, i.e. not changed when stored in the stack.

Fig. 5. Interrupt sequence

#### **Address Modifier**

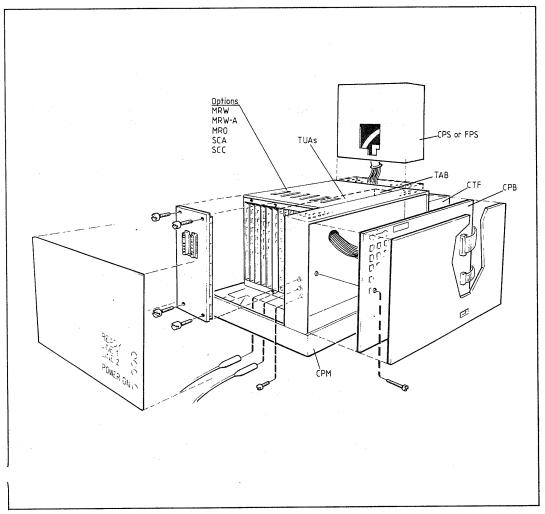

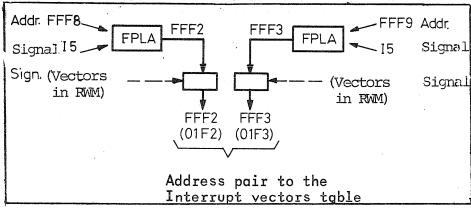

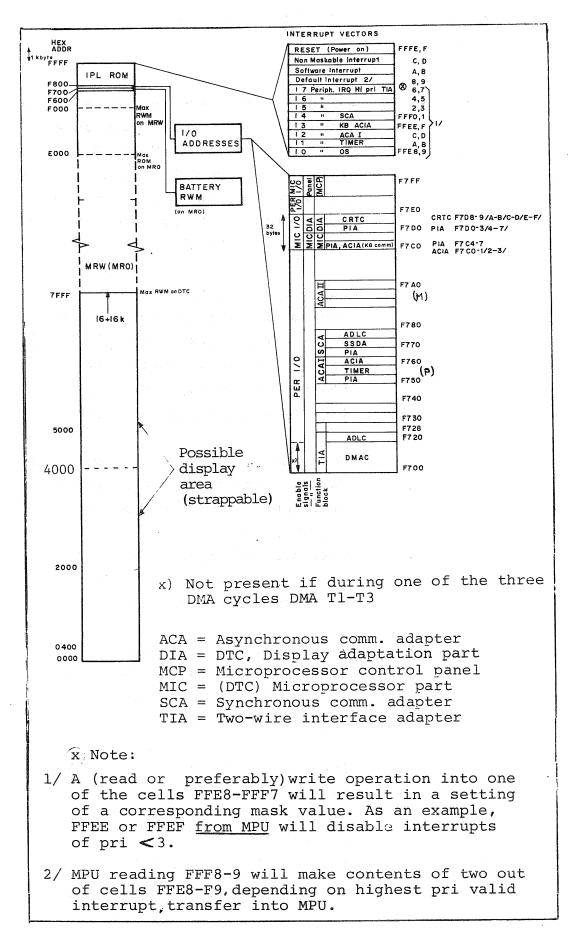

When the MPU addresses cells FFF8<sub>(16)</sub> and FFF9<sub>(16)</sub>, an address modifier will change the addresses to a pair of addresses in the area FFE8<sub>(16)</sub> – FFF7<sub>(16)</sub> depending on the highest priority valid interrupt in an interrupt register. That is to say, if the interrupt register still holds an interrupt with a level higher than or same as the actual mask level when FFF8<sub>(16)</sub> is applied, the MPU will fetch the address to that specific interrupt routine when addressing cells FFF8<sub>(16)</sub> and FFF9<sub>(16)</sub>. Note that address modification only occurs for addresses FFF8<sub>(16)</sub> and FFF9<sub>(16)</sub> from the MPU.

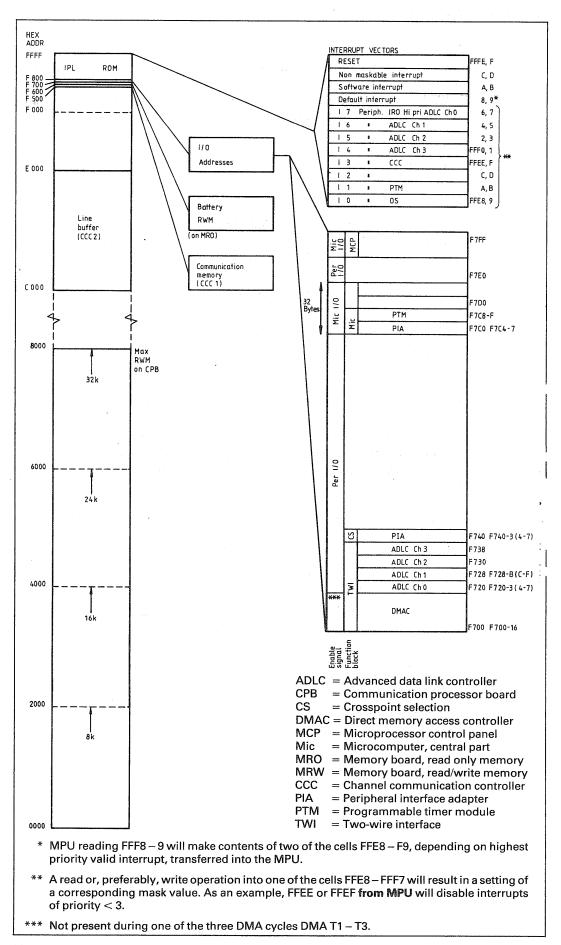

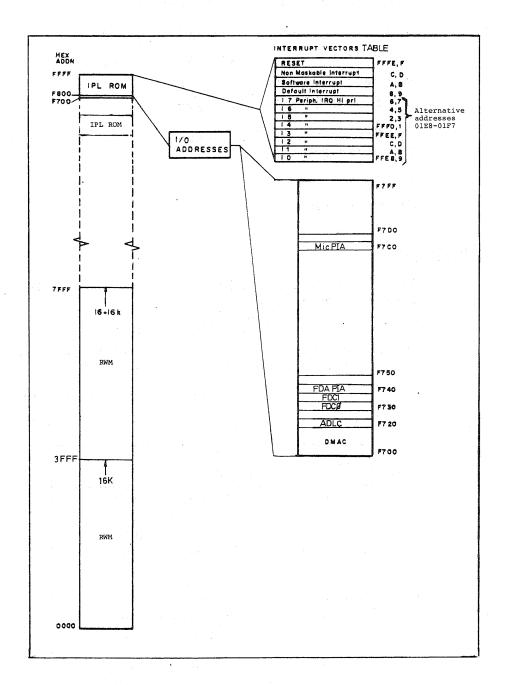

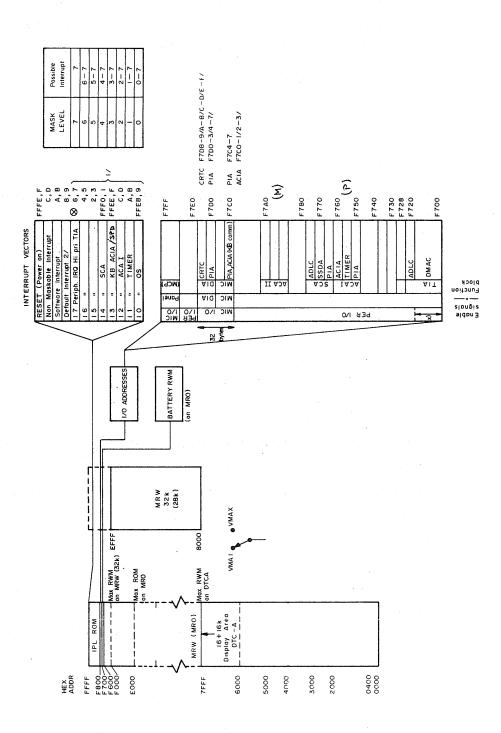

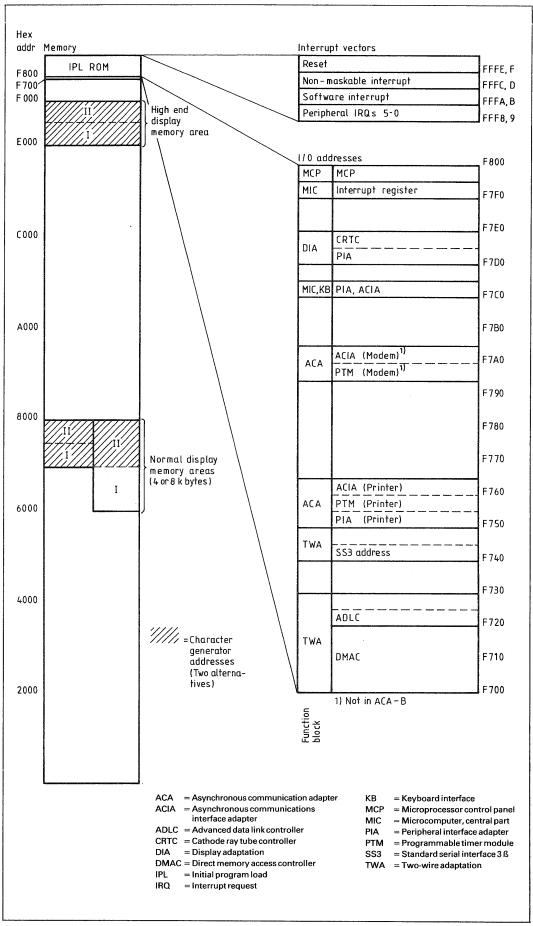

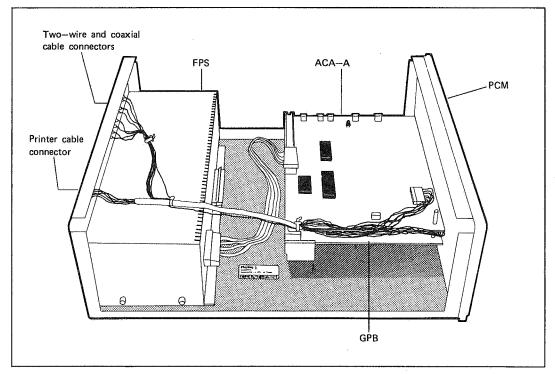

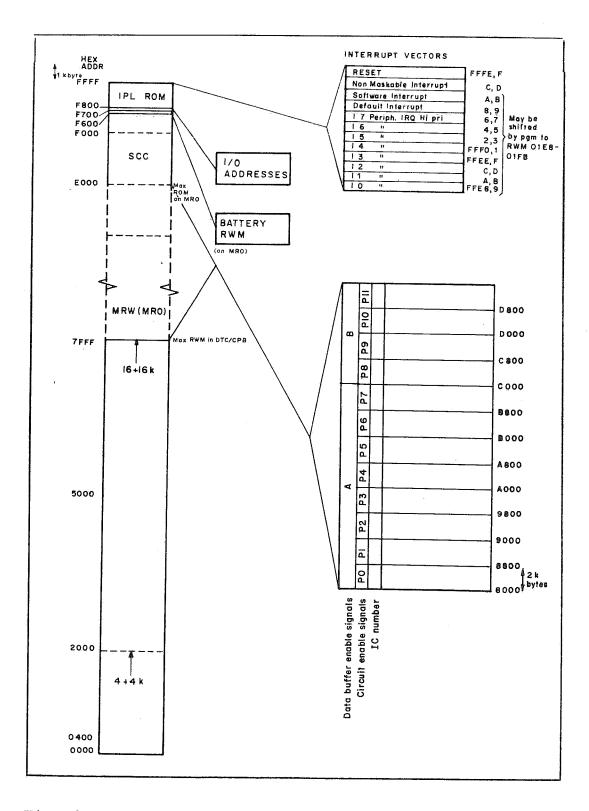

See Fig. 10 for detailed information on interrupt vector addresses.

#### Mask Register

The mask register is set to an associated value if a specific vector address in the area FFE8<sub>(16)</sub> to FFF7<sub>(16)</sub> is applied on the address bus from the MPU. If the MPU e.g. reads cell FFE8<sub>(16)</sub>, the mask will be set to zero and all interrupts will be permitted in case the MPU CCR I-bit is reset. No address modification will take place; the read operation will fetch the address to interrupt routine 0 to the MPU from the IPL ROM. If no change of the MPU register contents is wanted when setting the mask value, a write operation should be performed.

#### **Interrupt Register**

The interrupt register latches the state of the IRQs at the beginning of each  $\emptyset$ 2 period except when cells FFF8, 9, A, or B<sub>(16)</sub> (IRQ or SWI vector) are addressed by the MPU. The reason for not latching is that the modified address lines should be stable when the MPU fetches a vector.

#### **Generation and Direction of IRQs**

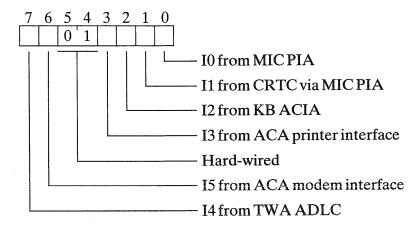

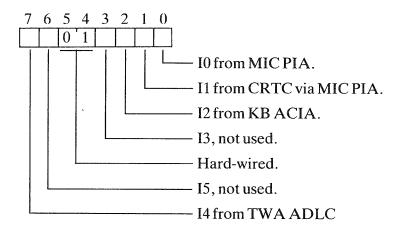

As mentioned above, there are eight possible incoming IRQs.

Several IRQs originate from sources where the IRQ is stable. The reset of such an IRQ, which has to be done before clearing the MPU I-bit, is generally performed by reading a specific register of the interrupting circuit.

Some interrupts may originate from circuits that only provide a short pulse that could disappear before the program is ready to be interrupted. To prevent this, at least one IRQ is coupled to the interrupt register via a latch. This latch may be reset by resetting a bit of a MIC PIA register (microcomputer peripheral interface adapter), but is unconditionally set when an interrupt occurs. Thus, if an interrupt line with a latch is used for stable interrupts, the MIC PIA bit should always be reset. Otherwise the IRQ in question would have to be reset by both reading a register of the interrupting peripheral and resetting the MIC PIA bit.

Interrupts may also be given by the microcomputer to the microprocessor of e.g. a connected synchronous communication controller (SCC). This is done when a bit of the MIC PIA peripheral register is set.

The specific use of the various interrupts in the different microcomputers of the system is described in the different chapters on the DU, FD, CPR etc. Detailed descriptions of the locations of the different interrupt vectors and addresses for mask setting is found in the memory maps.

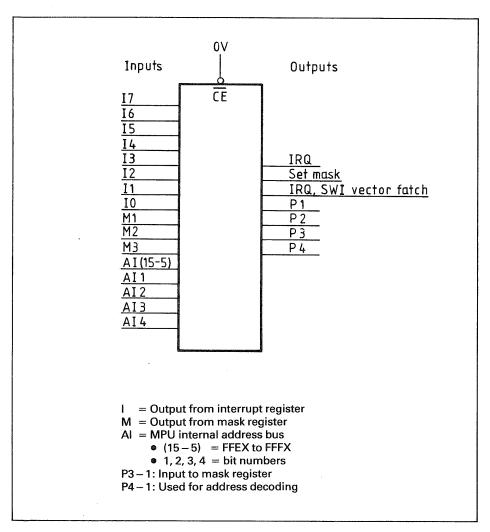

#### Interrupt Priority and Address modifier (FPLA)

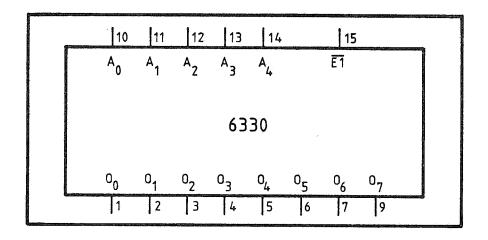

The interrupt priority control and address modification is made by an FPLA (field programmable logic array). See Fig. 6. The logic array is programmed to generate certain outputs in response to different combinations on the inputs. The programming is shown below:

| Activat                                  | ing inpu             | ıt combii                                                   | nations (pi                                            | n 19 = 0V)                                                                       |                                   | Activa | ited output                                           |  |  |  |  |

|------------------------------------------|----------------------|-------------------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------|--------|-------------------------------------------------------|--|--|--|--|

| Internal<br>address<br>4 3 2 1           | AI =<br>FFEX<br>FFFX | Mask<br>reg<br>3 2 1                                        | 1                                                      | upts from<br>atch<br>4 3 2 1 0                                                   | Signals Active Comments level     |        |                                                       |  |  |  |  |

| 1 1 1 1                                  | 0                    | Active I                                                    |                                                        | 0 0 0 0                                                                          | . *                               |        |                                                       |  |  |  |  |

| ××××                                     | ×                    | 0 0 0<br>0 0 1<br>0 1 0<br>0 1 1<br>1 0 0<br>1 0 1<br>1 1 0 | 1 1 1<br>1 1 1<br>1 1 1<br>1 1 1 1<br>1 1 0 2<br>1 0 X | 1 1 1 1 0* 1 1 1 0 X 1 1 0 X X 1 1 0 X X 1 0 X X X 0 X X X X X X X X X X X X X X | IRQ                               | Low    | Only valid interrupts<br>are signalled on<br>IRQ line |  |  |  |  |

| 0 1 X X<br>1 0 X X                       | 0                    | xxx                                                         | x x x                                                  | ××××                                                                             | Set mask                          | High   | FFE8-F<br>FFF0-7                                      |  |  |  |  |

| 1 1 0 X                                  | 0                    | xxx                                                         | XXX                                                    | xxxx                                                                             | IRQ, SWI<br>vector fetch**        | High   | FFF8-B                                                |  |  |  |  |

| 0 0 0 0<br>0 0 0 1<br>0 0 1 0<br>0 0 1 1 | ×                    | ×××                                                         | x x x :                                                | ××××                                                                             | P4-1=0000<br>0001<br>0010<br>0011 |        | No modification                                       |  |  |  |  |

| 0 1 0 0                                  | X<br>0               | X X X<br>0 0 0                                              | 1                                                      | X X X X X<br>1 1 1 1 0                                                           | 0100<br>0100                      |        | No modification<br>10 vector addr – FFE8, 9           |  |  |  |  |

| 0 1 0 1 1 1 0 0                          | X<br>0               | X X X<br>0 0 1*                                             | 1                                                      | X X X X X<br>1 1 1 0 X                                                           | 0101<br>0101                      |        | No modification<br>I1 vector addr – FFEA, B           |  |  |  |  |

| 0 1 1 0 1 1 0 0                          | X<br>0               | X X X<br>0 1 0*                                             |                                                        | X                                                                                | 0110<br>0110                      |        | No modification<br>I2 vector addr – FFEC, D           |  |  |  |  |

| 0 1 1 1 1 1 0 0                          | X<br>0               | X X X<br>0 1 1 <sup>x</sup>                                 | 1.                                                     | X                                                                                | 0111<br>0111                      |        | No modification<br>13 vector addr – FFEE, F           |  |  |  |  |

| 1 0 0 0 1 1 0 0                          | X<br>0               | X X X<br>1 0 0*                                             | 1                                                      | X                                                                                | 1000<br>1000                      |        | No modification<br>I4 vector addr – FFF0, 1           |  |  |  |  |

| 1 0 0 1                                  | X<br>0               | X X X<br>1 0 1 <sup>x</sup>                                 | 1                                                      | x                                                                                | 1001<br>1001                      |        | No modification<br>I5 vector addr – FFF2, 3           |  |  |  |  |

| 1 0 1 0                                  | X<br>0               | X X X<br>1 1 0*                                             |                                                        | x                                                                                | 1010<br>1010                      |        | No modification<br>16 vector addr – FFF4, 5           |  |  |  |  |

| 1 0 1 1 1 1 0 0                          | l .                  | I .                                                         | 1                                                      | x                                                                                | 1                                 |        | No modification<br>17 vector addr – FFF6, 7           |  |  |  |  |

| 1 1 0 0                                  | 1                    | 1                                                           |                                                        | X X X X X<br>narked I0-I7                                                        | 1100<br>1100                      | t .    | No modification<br>Default vector address             |  |  |  |  |

| 1 1 0 1<br>1 1 1 0<br>1 1 1 1            | Х                    | xxx                                                         | xxx                                                    | xxxx                                                                             | 1101<br>1110<br>1111              | 1      | No modification                                       |  |  |  |  |

<sup>1 = +</sup>TTL 0 = 0V X = Don't care \* or lower mask value \* or higher interrupt

<sup>\*\*</sup> Inhibits setting of the interrupt register

Fig. 6. FPLA inputs and outputs

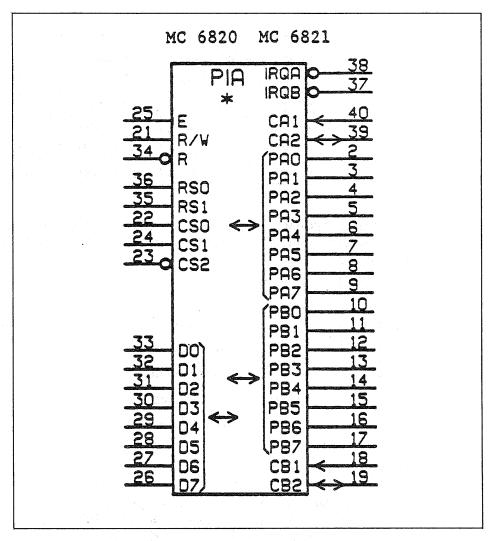

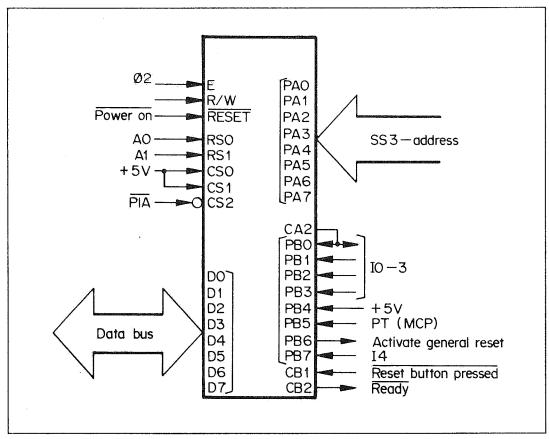

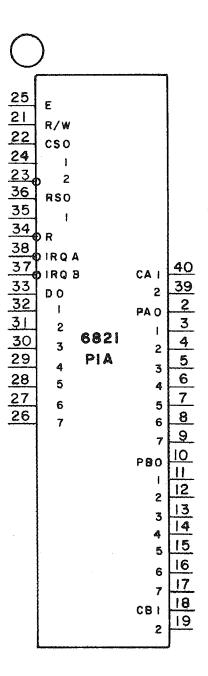

#### Peripheral Interface Adapter, PIA

A peripheral interface adapter, PIA, is used in several places in the equipment, but the hardware description is placed here in connection with the microcomputer PIA, MIC PIA, used for interrupt control. The programming of the MIC PIA is discussed together with the microprocessors of each specific unit as it varies between them.

#### Signals

The PIA is typically used as an adapter between the 8-bit MPU data bus (D 7 through 0, see Fig. 7) and two peripherals with parallel 8-bit interfaces. The peripheral pins (PA7-0 and PB7-0) can be individually programmed to work as outputs or inputs. Each side (A and B) has two peripheral control lines (CA1 and CA2/CB1 and CB2 respectively) with programmable functions and an associated interrupt request lines (IRQA/IRQB). The IRQ outputs can e.g. be or-wired to the MPU IRQ input or each one tied to a priority interrupt controller input if different interrupt levels are used and/or fast identification of the interrupt source is wanted.

Fig. 7. PIA drawing symbol

#### Registers

Each side of the PIA has three 8-bit registers associated with it. These are:

- Data direction register (DDR). If a bit in the DDR is one the corresponding peripheral line will function as an output.

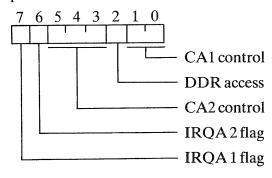

- Control register (CR), containing interrupt flags, interrupt mask and control, address control and control of the function of the peripheral control line CA2/CB2 (input or output).

- Peripheral register (P), containing data to/from the peripheral.

At reset all register contents are taken to zero.

The addressing of the six registers is made with the two register select lines RS1 and RS0 and one bit (bit 2) of the control register (to choose between DDR and peripheral register). At a specific time thus only four registers are available for the MPU as only two address lines are used:

| RS1 | RS0 | Con<br>Regis | itrol<br>ter Bit | Location selected         |

|-----|-----|--------------|------------------|---------------------------|

|     |     | CRA 2        | CRB 2            |                           |

| 0   | 0   | 1            | Х                | Peripheral Register A     |

| 0   | 0   | 0            | X                | Data Direction Register A |

| 0   | 1   | Х            | X                | Control Register A        |

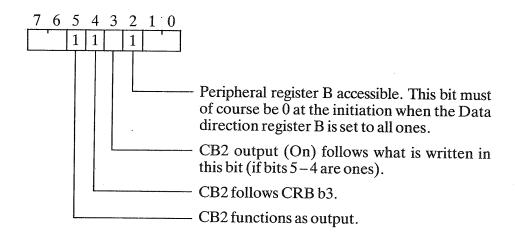

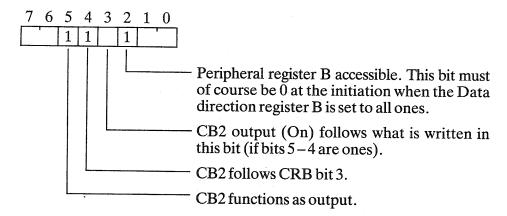

| 1   | 0   | Х            | 1                | Peripheral Register B     |

| 1   | 0   | Χ            | 0                | Data Direction Register B |

| 1   | 1   | X            | ×                | Control Register B        |

X = Don't care

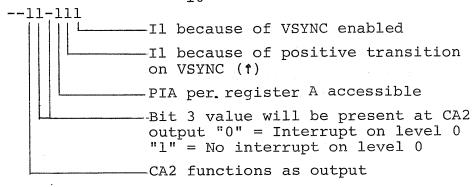

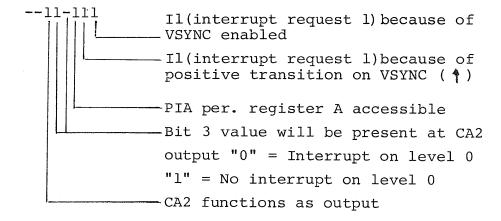

The control registers for the A and the B side are similar with one exception and the format is therefore only described for CRA with the exception pointed out:

#### Bit(s) Comments

- 7 IRQA 1, Interrupt flag, goes high on active transition of CA1 and is automatically cleared when the MPU reads the peripheral register A. It may also be cleared by hardware reset.

- 6 IRQA 2, Interrupt flag. When CA2 is established as input (b5 = 0): Goes high on active transition of CA2 and is automatically cleared when the MPU reads the peripheral register A. It may also be cleared by hardware reset.

When CA2 is established as output (b5 = 1): IRQA 2 = 0, not affected by CA2 transitions.

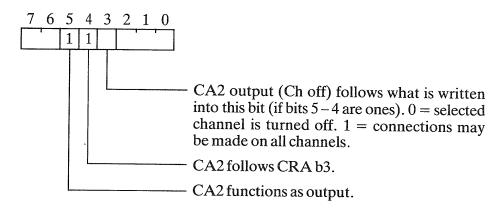

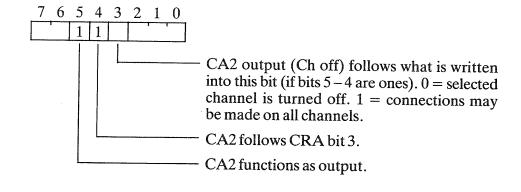

5-3 CA2 (CB2) established as output by b5 = 1

b3 = 1: Read strobe with E restore. CA2 goes low on the first high-to-low E transition following an MPU read of peripheral register A and is returned high by the next high-to-low E transition.

|   | CB2. The output functions of CB2 will not         |

|---|---------------------------------------------------|

| • | be similar to the same of CA2 when the            |

|   | control register B b5 – $4 = 10_{(2)}$ . They are |

|   | therefore inserted below:                         |

- b3 = 0: Write strobe with CB1 restore.

CB2 goes low on the first low-tohigh E transition following an

MPU write into peripheral register

B and is returned high by the next

active CB1 transition.

- b3 = 1: Write strobe with E restore. CB2 goes low on the first low-to-high E transition following an MPU write into peripheral register B and is returned high by the next low-to-high E transition.

| b5 | b4 | b3 |                                                                                 |

|----|----|----|---------------------------------------------------------------------------------|

| 1  | 1  | 0  | Reset CA2. CA2 goes low when the MPU writes $b3 = 0$ into the control register. |

|    |    | 1  | Set CA2. CA2 goes high when the MPU writes b3 = 1 into the control register.    |

#### CA2 established as input by b5 = 0

| b5 | b4         | b3 |                                                                                                                                                                                                                            |

|----|------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | X          | 0  | CA2 interrupt request disable. Disables IRQA MPU interrupt by CA2 active transition. IRQA will occur on the next (MPU generated) positive transition of b3 if CA2 active transition occurred while interrupt was disabled. |

|    |            | 1  | CA2 interrupt enable. Enables IRQA MPU interrupt by CA2 active transition.                                                                                                                                                 |

| b5 | b4         | b3 |                                                                                                                                                                                                                            |

| 0  | 0          | X  | Active CA2 transition. IRQA 2 set by high-to-low transition on CA2.                                                                                                                                                        |

|    | . <b>1</b> |    | Active CA2 transition. IRQA 2 set by low-to-high transition on CA2.                                                                                                                                                        |

- 2 Determines whether the data direction register or the peripheral register is addressed

- 0 =Data direction register is selected.

- 1 = Peripheral register is selected.

- 1 Determine active transition on CA1 input for setting interrupt flag IRQA1 (CRA bit 7)

- 0 = IRQA is set by high-to-low transition on CA1.

- 1 = IRQA is set by low-to-high transition on CA1.

- 0 CA1 interrupt request enable/disable

- 0 = Disable IRQA MPU interrupt by CA1 active transition. IRQA will occur on the next (MPU generated) positive transition of b0 if CA1 active transition occurred while interrupt was disabled.

- 1 = Enable IRQA MPU interrupt by CA1 active transition.

#### Timing

#### **Basic Timing**

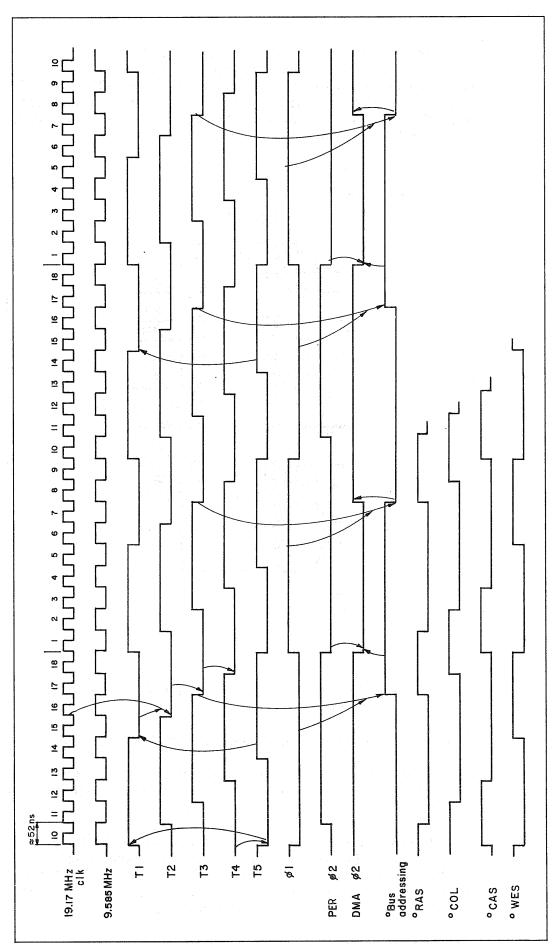

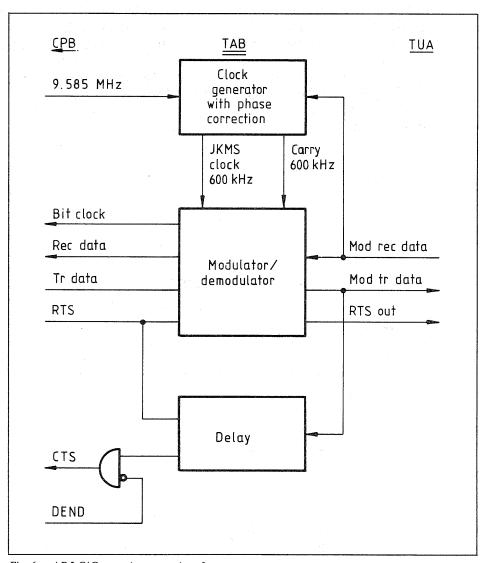

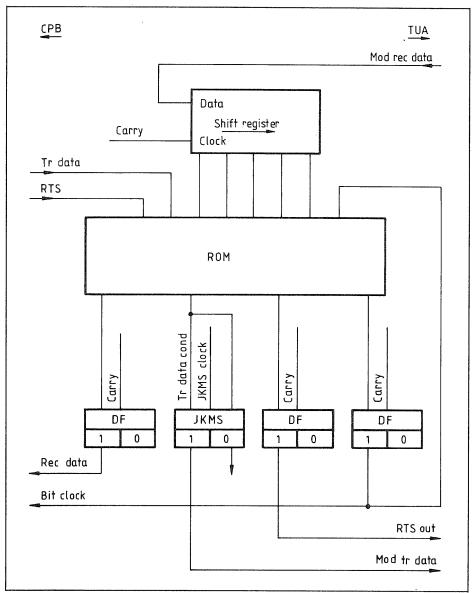

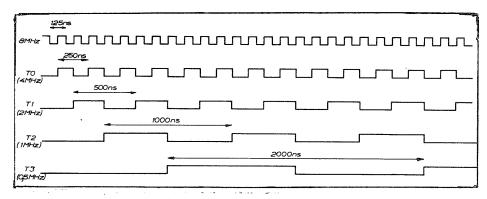

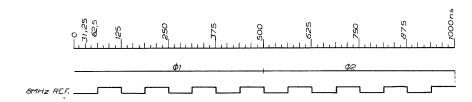

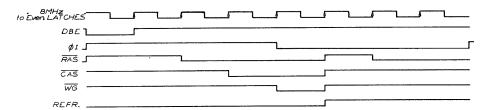

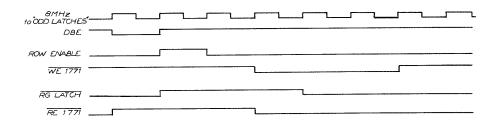

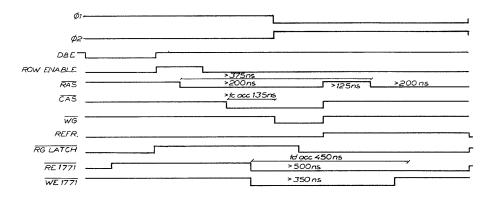

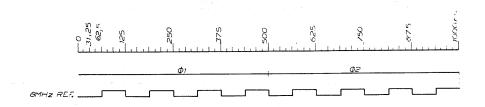

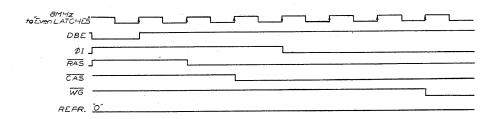

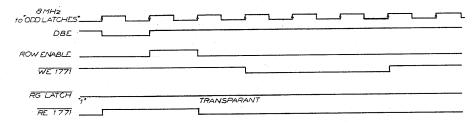

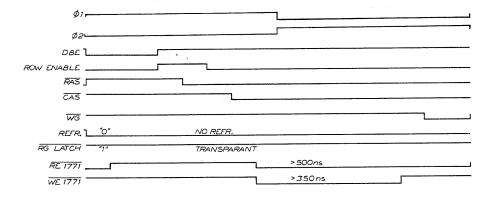

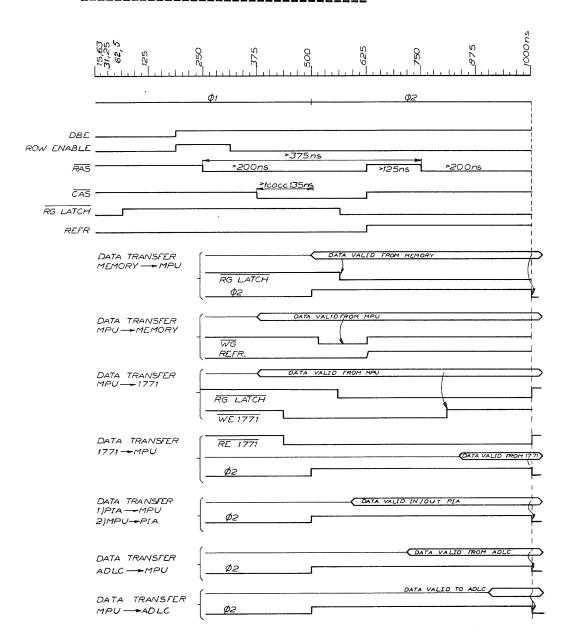

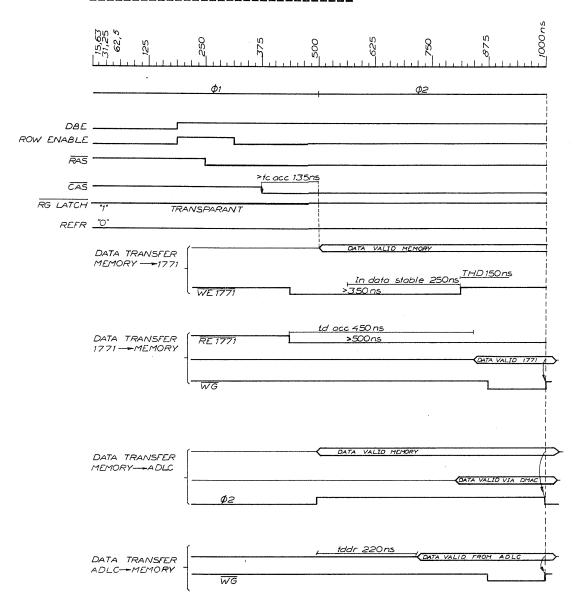

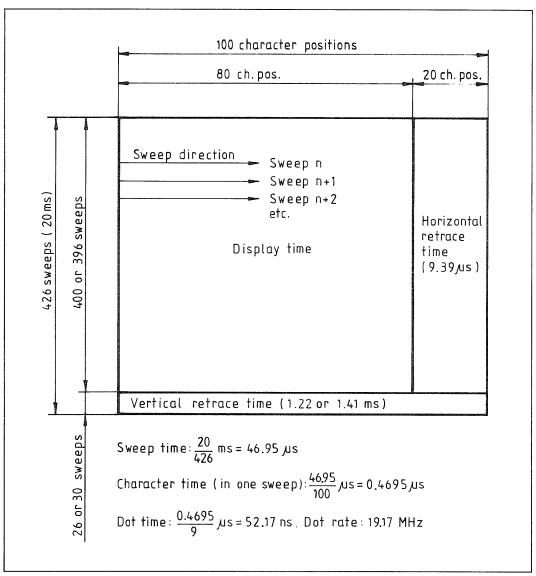

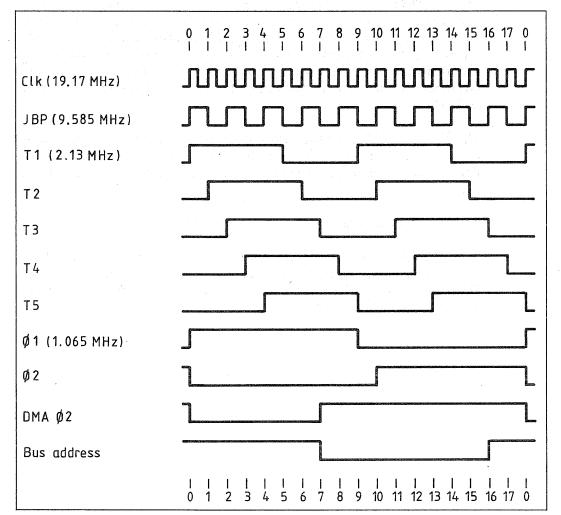

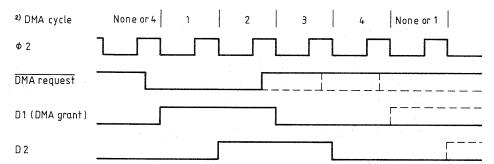

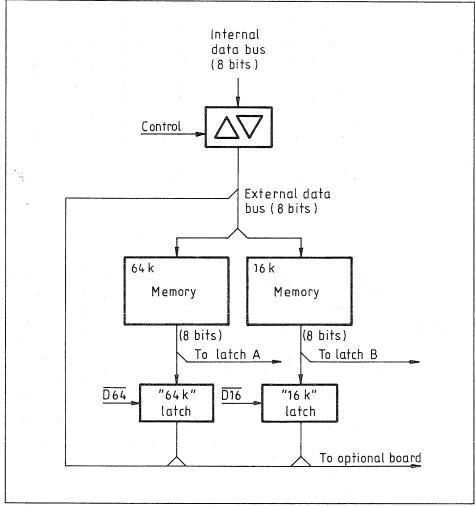

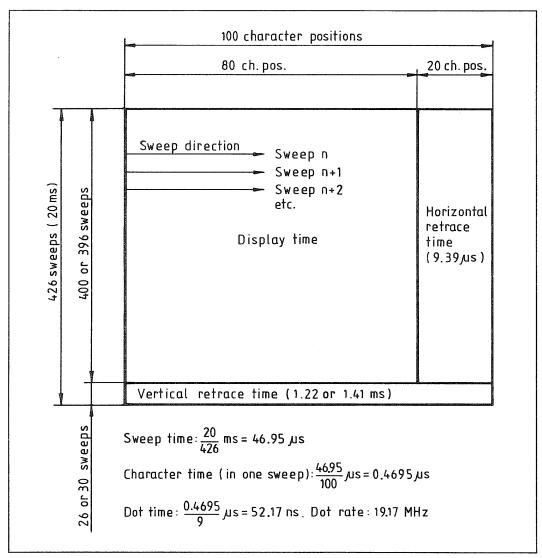

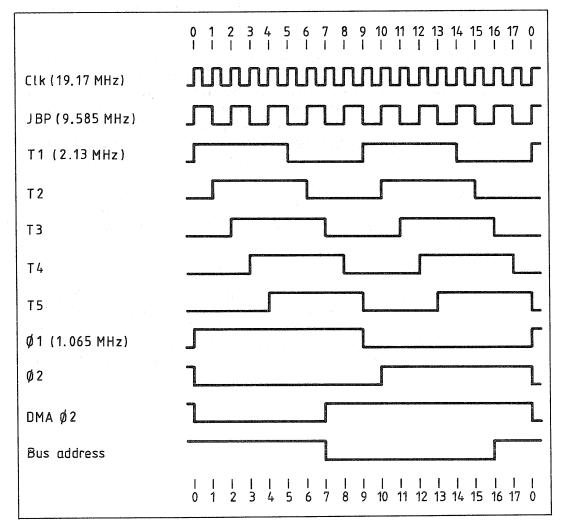

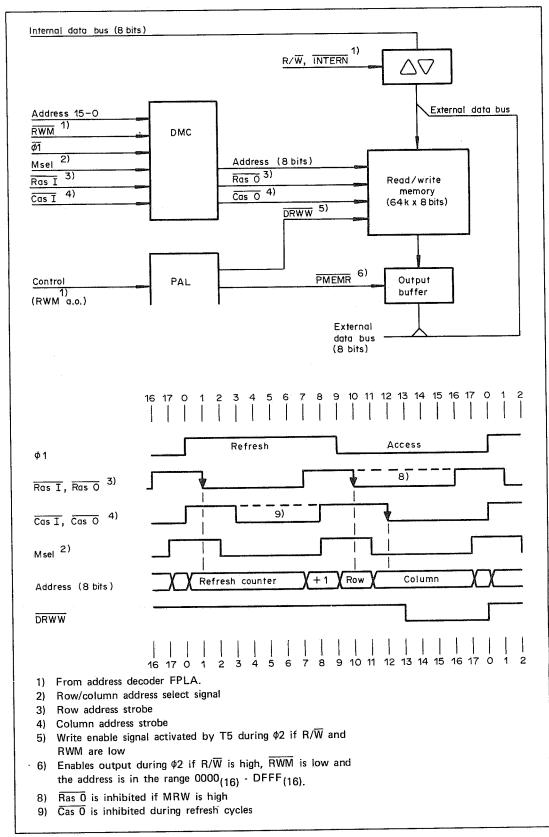

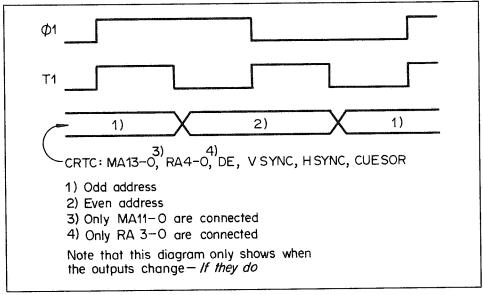

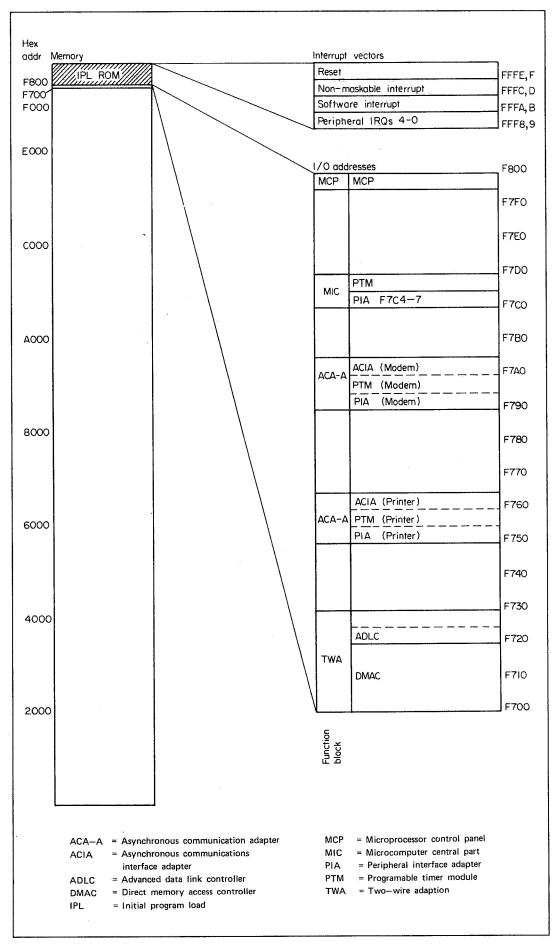

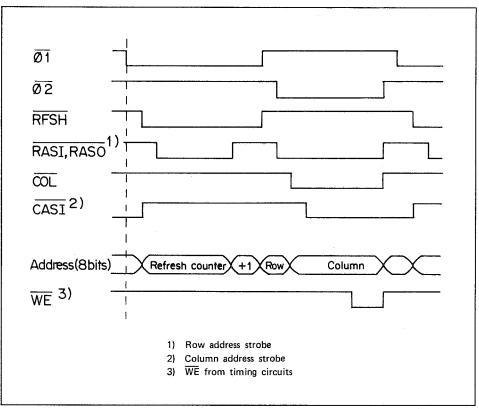

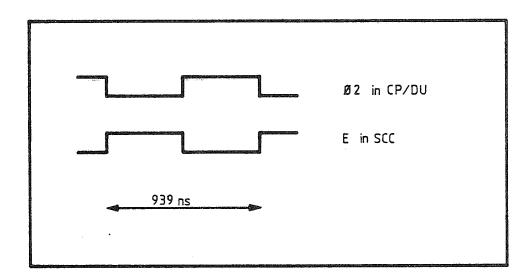

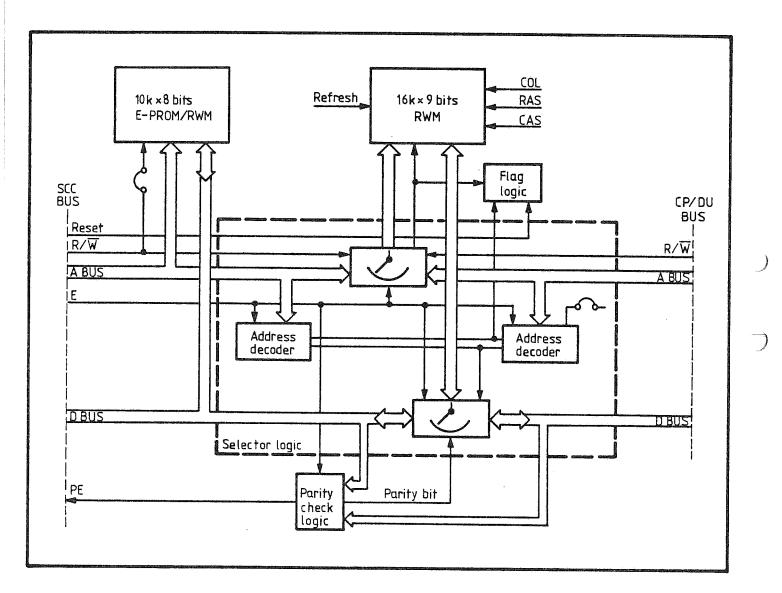

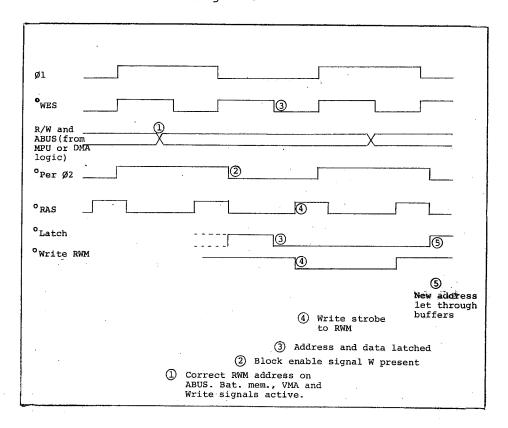

A basic 19.17 MHz clock signal is generated by a crystal clock. From this clock signal all timing signals, e.g. dynamic memory timing, two-wire transfer bit clock etc. are derived. Five 2.13 MHz clocks are generated (T1 – T5). Combinations of these are used to define different points of time during each half of the system clock period. The system clock,  $\emptyset$ , (microprocessor instruction clock) has a frequency of 1.065 MHz. It appears in several phases and with different pulse-pause ratios to compensate for propagation delays etc. The relations between the basic timing signals are shown in Fig. 8. Of the signals in Fig. 8; 9.585 MHz,  $\emptyset$  signals, RAS, COL, CAS and WES appear on buses connecting different logic boards.

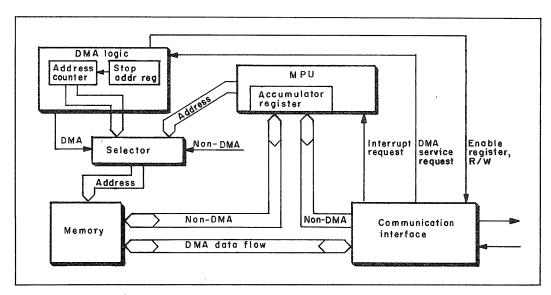

The MPU demands two non-overlapping complementary clocks. Circuitry is added to provide these; MPU  $\emptyset$ 1 and MPU  $\emptyset$ 2. These two clock signals together with the data bus enable signal (DBE) for the MPU (Observe that these three signals are only fed to the MPU.) differ from the other  $\emptyset$  signals in that they may be frozen (in the  $\emptyset$ 1 state) by a stretch signal. This signal is generated under certain conditions during a direct memory access (see Direct Memory Access).

#### Bus Timing Example

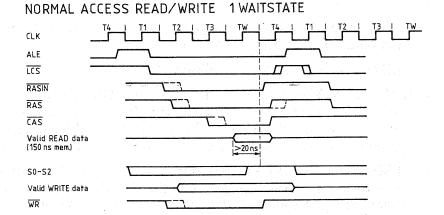

Consider the case when the MPU reads data from the basic read/write memory area.

- During Ø1 MPU puts out the new address and read level on the R/W line

- DMA Ø2 will enable a ROM used for memory address decoding. An enable signal for one of the memory blocks will then be produced. During this time the memory address from the MPU will be applied and used as row address and column address to the RWM. The generation of row address strobe, selection of column address and generation of column address strobe is governed by the RAS, COL and CAS signals respectively.

- The internal and external data buses will be connected during  $\emptyset 2$ . At the falling edge of  $\emptyset 2$  the data will be read into the MPU.

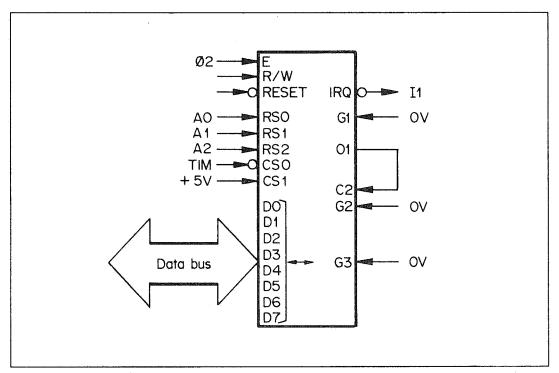

#### Programmable Timer Module, PTM

A programmable timer module, PTM, is sometimes tied to the micro-computer in order to avoid timing loops in the program.

Fig. 8. Basic timing signals

Signals

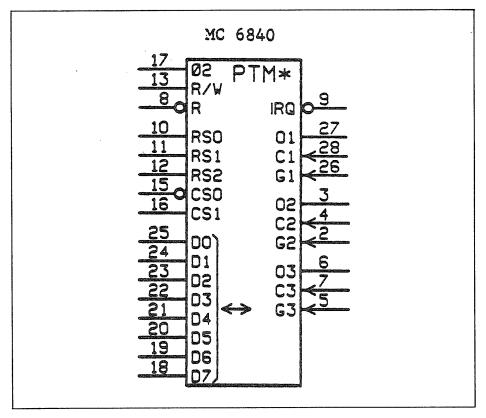

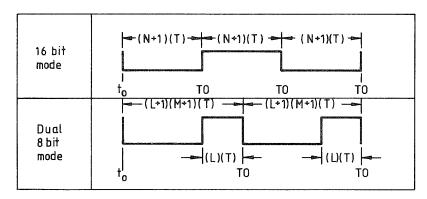

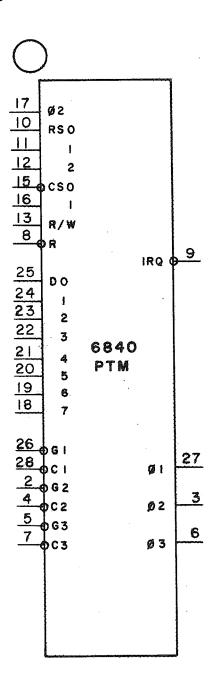

The programmable timer module contains three 16-bit counters. Each one of these may be programmed to produce symmetric or asymmetric square waves (or single shots) at the respective outputs O1, O2, and O3 and also interrupts on an IRQ output. See Fig. 9. The clock signal for a specific counter may be selected to be either the  $\emptyset$ 2 signal or a unique clock signal (C1, C2, and C3 respectively).

Fig. 9. PTM drawing symbol

RS2, RS1, and RS0 are used together with the R/W input for register addressing. See below.

D7 through 0 are used for connection to an 8-bit bidirectional data bus.

G1, G2, and G3 are used as enable signals for the three counters. When a G input goes low, the associated counter will be restarted (if the PTM is not reset).

A low level on the reset (R) input will stop all counters and reset the O1, O2, O3, and IRQ outputs as well as all status and control register bits but the internal reset bit. Furthermore, both the latches (see below) and the counters of all three timers will be preset to maximum values, and thus, if not reprogrammed before release, make the longest possible count cycle.

CS1 and 0 are the chip enable signals, needed to transfer data to or from the PTM.

#### Registers

The PTM contains one control register for each timer and one status register. Each timer contains a 16-bit timer latch (write only) and an associated 16-bit counter. The register addresses are listed below:

| Address inputs |     | nputs | Accessed register                                                      |                            |  |

|----------------|-----|-------|------------------------------------------------------------------------|----------------------------|--|

| RS2            | RS1 | RS0   | Write (R/W = 0)                                                        | Read (R/W = 1)             |  |

| 0              | 0   | 0     | Control register 3 (if CR2:0 = 0)<br>Control register 1 (if CR2:0 = 1) | No register<br>No register |  |

| 0              | 0   | 1     | Control register 2 (CR2)                                               | Status register (SR)       |  |

| 0              | 1 1 | 0     | MSB buffer (timer 1)                                                   | Timer 1 counter MSB        |  |

| 0              | 1   | · 1   | Timer 1 LSB latches*                                                   | LSB buffer (timer 1)**     |  |

| 1              | 0   | Ò     | MSB buffer (timer 2)                                                   | Timer 2 counter MSB        |  |

| 1              | 0   | 1     | Timer 2 LSB latches*                                                   | LSB buffer (timer 2)**     |  |

| 1              | 1   | 0     | MSB buffer (timer 3)                                                   | Timer 3 counter MSB        |  |

| 1              | 1   | 1     | Timer 3 LSB latches*                                                   | LSB buffer (timer 3)**     |  |

- \* When writing the LSB latches of a specific timer, the contents of the MSB buffer will be transferred to the MSB latches of that timer.

- \*\* After reading the MSB of a specific timer counter, the LSB buffer will, when read, present the contents of the LSB of that specific counter.

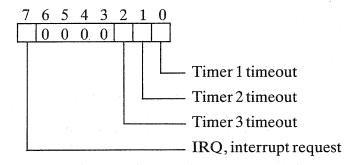

The interpretation of the status register (SR) bits is shown below:

Timeout of a counter always sets the associated status bit (SR:2, 1 or 0). It sets SR:7 only if bit 6 of the associated control register is 1.

All status bits are cleared when the PTM is reset. A status bit that is present when the status register is read will be cleared by a following read timer counter command.

A specific timeout flag (status bit) is also cleared by an initialization or a write operation into the timer latches of the associated timer.

The interpretation of the control register bits is summarized below  $(CRX = control\ register\ associated\ with\ timer\ No.\ X)$

| Bit No.                     | Bit name                 | Function if = 1                                                          | Function if = 0                                                                         |

|-----------------------------|--------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| CRX:7                       | Output<br>enable         | Output (O1, O2, or O3) enabled                                           | Output masked                                                                           |

| CRX:6                       | Interrupt<br>enable      | SR:7 and IRQ<br>enabled                                                  | No indications on SR:7 or IRQ output                                                    |

| CRX:5<br>(if CRX:<br>3 = 0) | Mode<br>control          | Single shot operation (Reinitialization needed for repetitive operation) | Continuous (cyclic)<br>count operation                                                  |

| CRX:4<br>(if CRX:<br>3 = 0) | Initialization<br>select | GX input going low restarts counter (See also CR1:0 = 1)                 | A write operation into the timer X latches (or GX ↓ or CR1:0 = 1) will initialize timer |

| CRX:3                       | Mode<br>control          | Frequency/pulse width comparison mode                                    | Continuous/single shot mode                                                             |

| CRX:2                       | Counting mode            | Dual 8-bit counting<br>mode*                                             | 16-bit counting mode*                                                                   |

| CRX:1                       | Clock<br>select          | Timer X counter uses clock on Ø2 input                                   | Timer X counter uses clock on CX input                                                  |

| CR3:0                       | Timer 3 clock<br>control | Timer 3 clock is divided by 8 before applied to the counter              | Timer 3 clock functions as the other clocks                                             |

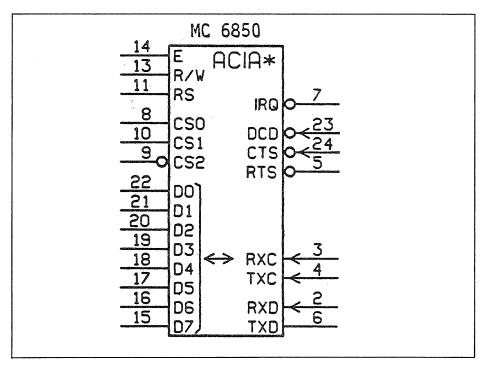

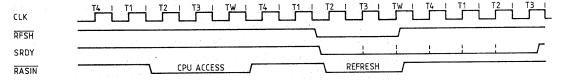

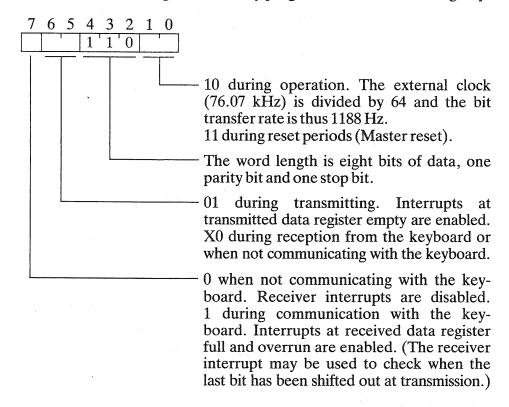

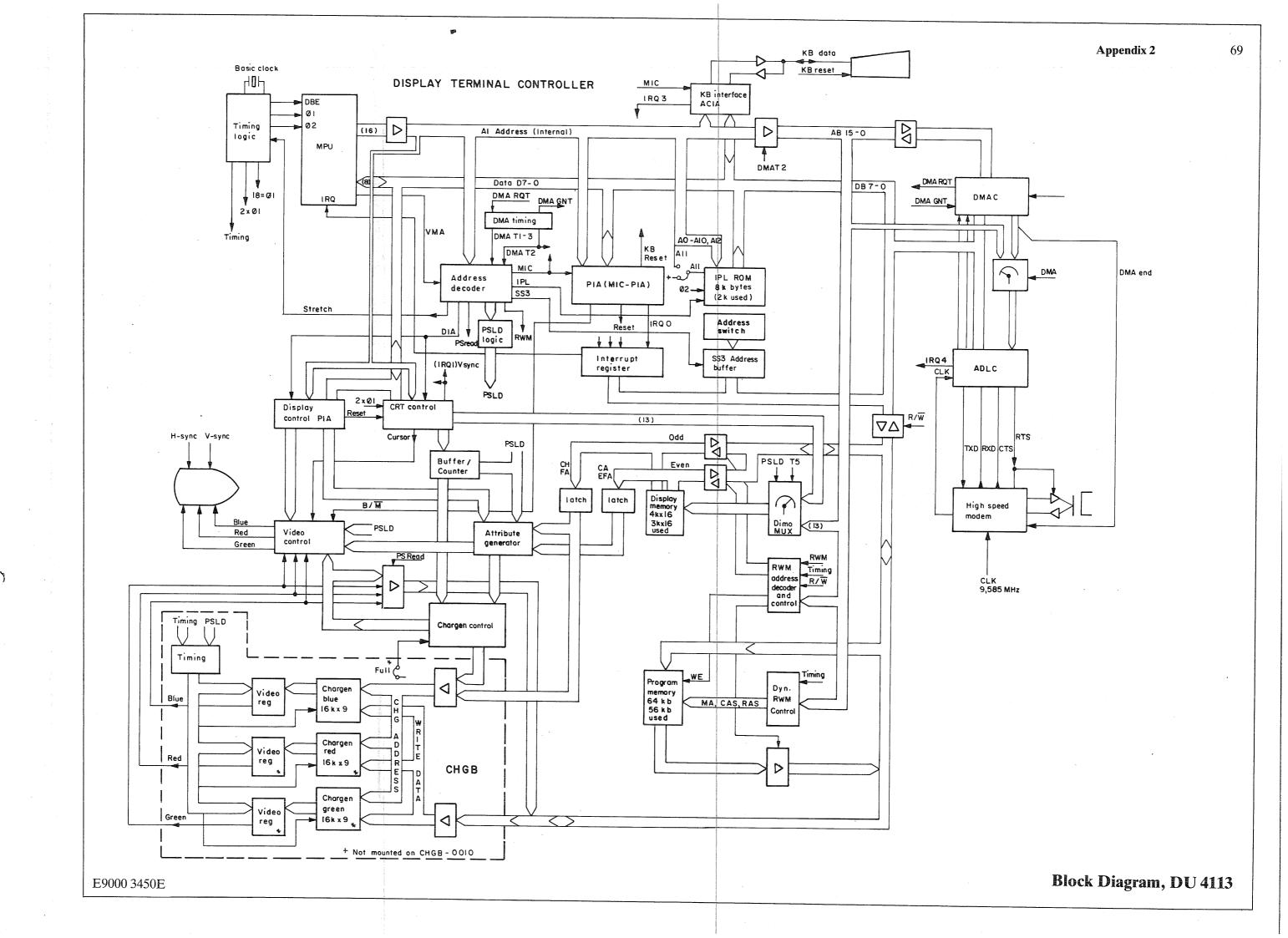

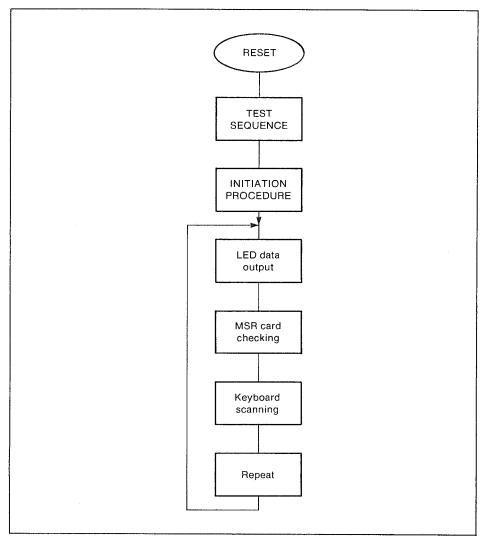

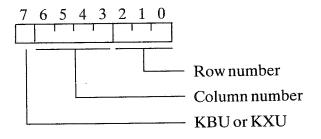

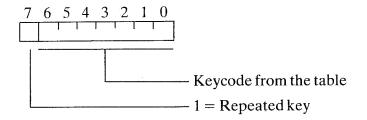

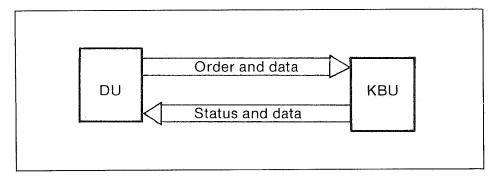

| CR2:0                       | Control reg.<br>address  | CR1 may be written                                                       | CR3 may be written                                                                      |